请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:ADC12DJ3200 工具与软件:

您好!

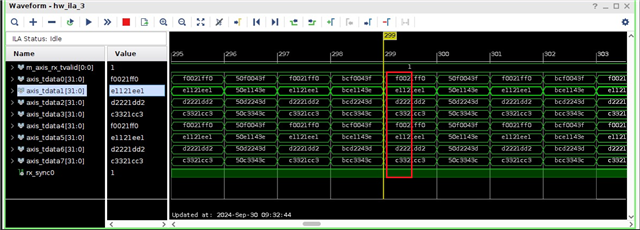

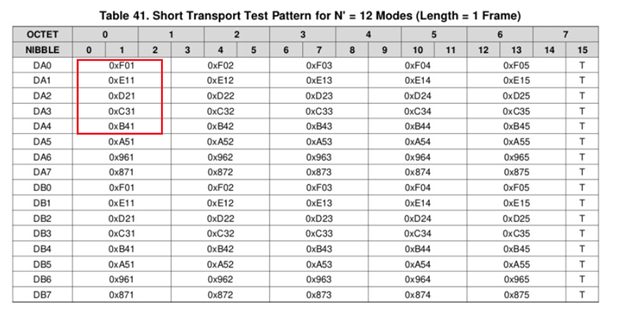

我的客户在尝试在测试模式下使用 DJ3200时遇到问题。 他们尝试在 N'=12的情况下进入测试模式、他们为每个通道捕获的数据如图1所示。 DA0-DA3的图形从 F00/E11/D22/C33开始、而不是数据表中显示的 F01/E11/D21/C31。 我的客户是否正确进入测试模式? 是否还有其他需要配置的东西、或可能导致客户方案的任何原因?

请对此提出一些建议、谢谢。

BR、

制造商