工具与软件:

您好!

ADS1282-SP 数据表修订版中的集成电路 b 第9页的第7.7节定义了参数 TDR。

下面您可以看到针对 sinc 滤波器的表21引用、而为 FIR 滤波器分别提供了一个公式(我认为将把这些公式组合在一起、使两个滤波器获得相同的 TDR)

我的问题是如何计算每个滤波器的 TDR?

BR、Hang

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

ADS1282-SP 数据表修订版中的集成电路 b 第9页的第7.7节定义了参数 TDR。

下面您可以看到针对 sinc 滤波器的表21引用、而为 FIR 滤波器分别提供了一个公式(我认为将把这些公式组合在一起、使两个滤波器获得相同的 TDR)

我的问题是如何计算每个滤波器的 TDR?

BR、Hang

您好 Hang、

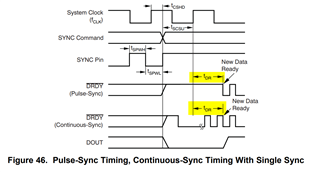

图46中的 TDR 是相对于 SYNC 引脚或 SYNC 命令定义的。

在 sinc+FIR 滤波器组合的情况下、您可以计算数据表中提供的 TDR 值:

TDR=62.98046875/Fdata + 466/fCLK

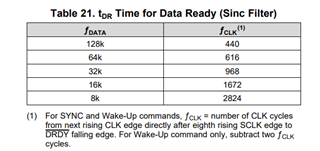

表21中提供了 SINC 滤波器 TDR 值:

TDR 基于多个数据速率周期、外加取决于 IC 内部数字设计细节的开销(fCLK 周期)。 提供的值已由数字设计确定并通过测量进行了验证。 在使用 sinc 滤波器时、要获得精确的 TDR 值、没有一个简单的公式可用于根据数据速率进行计算。

此致、

Keith Nicholas

精密 ADC 应用

尊敬的 Keith:

感谢您的快速支持! 如果您还能回答下面的另外2个问题、将不胜感激:

fCLK 取决于用户提供的时钟、表5中针对 sinc 定义了 fdata、表6中针对 FIR 定义了 fdata、表8中针对 HPF 定义了 fdata。

使用 sinc+FIR 滤波器时、鉴于 fClk = 4.096Mhz、我认为应从表6中选择 Fdata (假设选择的速率为1000SPS)

那么公式为 TDR=62.98046875/Fdata + 466/fCLK = 62.98046875 * 1ms + 466 * 244.14ns。

这里的计算结果是否正确?

2.仅使用 sinc filer 时、可以直接从表21中提取 TDR (但不用作精确值)

假设 fClk = 4.096Mhz、并且从表5中选择8000SPS 的 Fdata、则 TDR 约为2824 * 244.14ns。

这里的计算结果是否正确?

3.表5、表6和表8是在假设系统时钟= 4.096Mhz 的情况下绘制的、与8.1.14相符:

"...数据转换速率与 CLK 频率直接相关..."

这意味着、如果我使用2.048Mhz、那么数据速率将相应地减半、我的理解是否正确?

此致、

Hang Lin

您好 Hang、

1. 是的,您的计算是正确的。 表5和表6中的数据速率仅对4.096MHz 有效。 如果需要在表5和表6中计算不同 fCLK 频率的数据速率、则 Fdata=fCLK/(4*N)、其中 N 是抽取率。

HP 滤波器仅与 sinc+FIR 搭配使用、并遵循表6中的数据速率。 表8只是几个示例。 使用 sinc+FIR+HP 时、可将数据速率设置为表6中的任意值:250,500,10010002000 或4000SPS。

2. 是的、您对 TDR、sinc 滤波器、8000SPS 的计算正确。

3. 是的、如果2.048MHz、数据速率将为1/2。 fdata=fclk/(4*N)将始终为不同 CLK 频率和抽取率(N)提供正确的数据速率。

此致、

Keith