工具与软件:

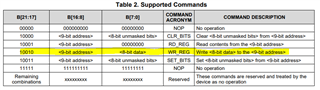

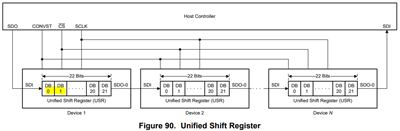

我们使用3个菊花链 ADS8924BGER 完成了一项设计。 我们将使用 STM32 µcontroller 来读出转换后的数据。 由于 μ µC SPI 外设中存在某些不可预见的硬件限制、我们只能读出64位(因此仅发送64个 SCLK 脉冲)。 数据表中菊花链拓扑章节下有一条注释:"较短的数据传输帧(帧中的 SCLK 数量< 22 × N)可能会导致器件配置错误、必须避免"。 除了偏移校准(3V3参考)之外、所有配置寄存器在我们的设置中都具有默认值。 在采用该配置的初始测试中、未观察到任何错误。 是否有人能提供有关 "错误设备配置"的更多信息以及如何检测这些错误?