工具与软件:

大家好、团队成员:

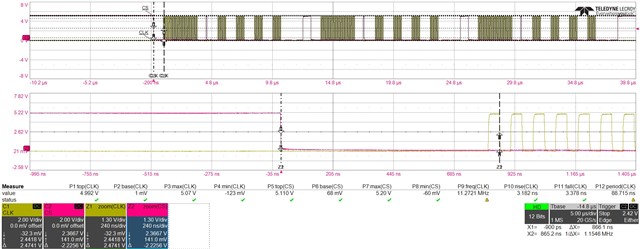

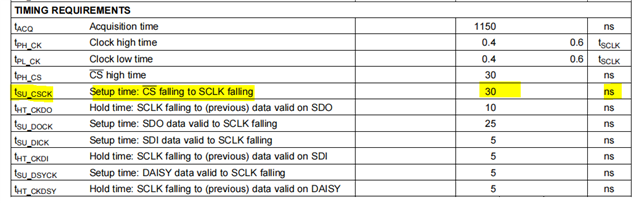

我的客户测试了 ADS8688并发现 TSU_CSCK 比 pic 低30ns 以上。 在数据表中、 TSU_CSCK 的最小值为30ns、您可以在第二个 pic 中找到它。

为什么会这样?

BR、

月亮

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.