工具与软件:

我们公司的控制器输出 SCLK 并将其输入到 ADC108S102。

请参见图2。 ADC108S102数据表中的 ADC108S102串行时序图。

它似乎在上升沿锁存 DIN、在下降沿输出 DOUT。

但是、当 ADC108S102输出 DOUT 时、它不是"从控制器接收到的 SCLK 上升沿"。 是否规范是根据来自控制器的 SCLK 的"上升沿"在 ADC108S102中创建下降边沿时序、并且 DOUT 在该时序上被输出?

换句话说、ADC108S102侧是否使用 SCLK 的下降边沿进行控制?

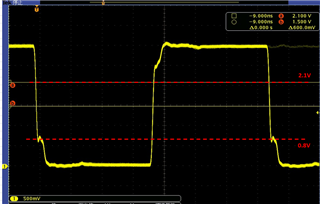

作为您问题的背景、当我们观察我们公司基板的波形时、我们在 SCLK 的下降沿观察到了一个轻微跃升的波形。

然而、如果你不使用下降沿进行控制、我想你不需要担心这个步骤、所以我这次问过你。