Other Parts Discussed in Thread: ADS131E08

工具与软件:

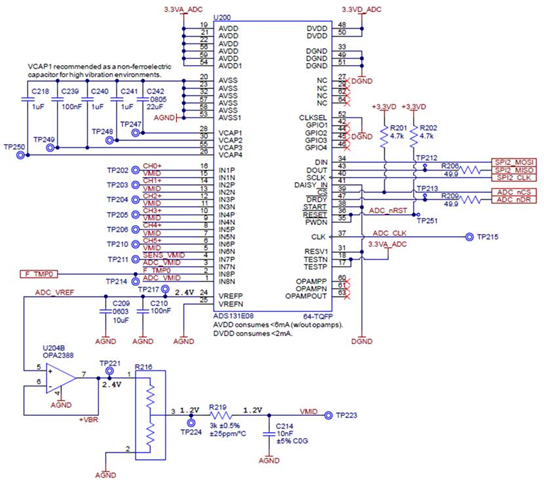

我们有一个想要利用 ADS131E08 ADC 全24位范围的设计。 我们预计整个范围为+/-2^23位=+/-8,388,608。

我们使用的正输入电压范围为0 ~ 2.4V、并且每个通道具有1.2V 的固定负电压。 这样、此差动输入电压范围为+/-1.2V、通过使用= 2的内部 ADC 增益、我们可实现约+/-2.4V 的差动输入电压范围。

简单地说、我们的问题是、我们看到 ADC 值在我们达到差分输入的界限之前卡住了。 当我们通过在正输入通道上施加2.4V 或0V 电压来强制输入达到饱和状态时、ADC 输出不会达到+/-8M。

我们在两种设计上看到过这种行为。 首先、我们为 ADC 提供3.3AVDD、并将 AVSS 连接到0V GND。 在上、第二个 AVDD 连接到3.0V 而不是3.3V。 在第一种情况下、我们确实在正端看到+8388607、但在负端绝不会达到-8388608 在第二种情况下、我们在负端或正端没有达到8M。

能否帮助我了解发生这种情况的原因以及我们如何在用例中利用完整的24位范围?