主题中讨论的其他器件:OPA1652、 OPA1602、BUF634、 TINA-TI、OPA1612、 OPA1656、 OPA1642、 DAC11001B

工具与软件:

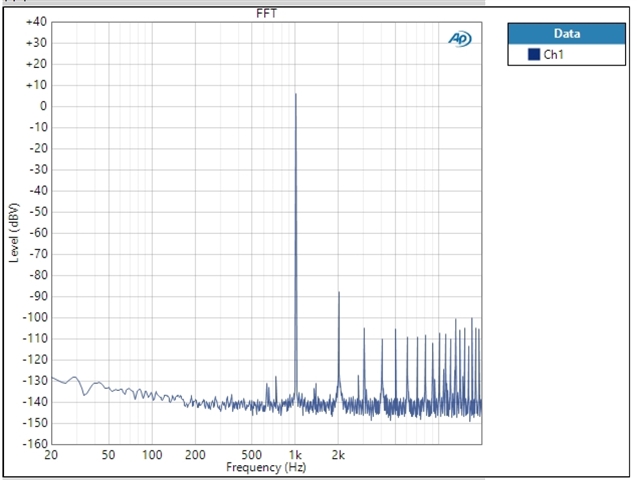

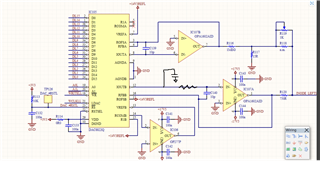

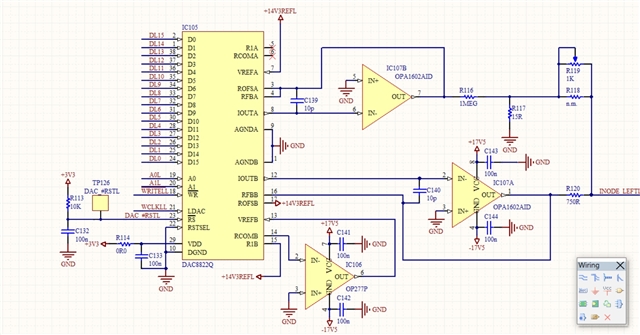

大家好、我将在高分辨率音频应用中使用 DAC 8822、如随附的原理图所示。 8822由 FPGA 驱动、附加原理图中电路的输出连接到作为反相加法器使用的运算放大器的反相输入。 虽然我已经达到了分辨率、采样频率和信噪比(SNR)方面的目标、但是总谐波失真+噪声(THD)+N 远远高于预期。 请注意、我最大限度地减少了辅助电路的主要过零干扰、残余干扰杂散远低于 THD 谐波。

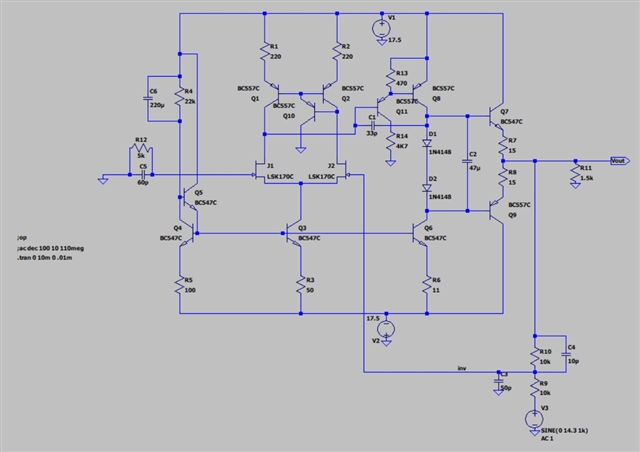

我发现导致 THD 过大的一个原因是最初用作8822 (OPA1652)的 I/V 转换器的运算放大器的有限 GBW。 用 OPA1602代替后、THD 降低了6dB。 为了检查是否需要进一步的 GBW、我降低了 VREF 值、期望 THD 进一步降低、但这没有发生、因此我认为 OPA1602是可以的。

DAC 电路的 THD @ 0dBFS 现在为0.002%、我的目标是降低大约20dB。 奇怪的是、IC107A 中的 THD ("粗略"DAC")与其完全相同。 我期望第二个("精细"DAC")(我用于"细化"第一个 DAC 的波形、它正常工作、就像检查波形@-91dB 时、我仍然看到具有1% LSBpp +N 而不是总 THD 方波的漂亮正弦波)有助于保持 THD 较低、但这不会发生。

所以我认为这个问题主要跟第一个 DAC 有关。 有没有任何实用方法可以降低第一个("总") DAC THD? 这是否与双极零误差、满量程误差等参数有关?

感谢你的帮助。