工具与软件:

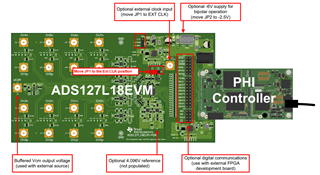

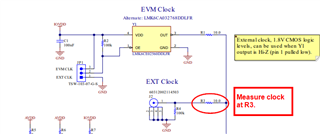

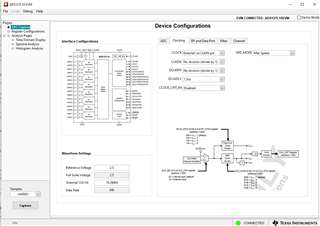

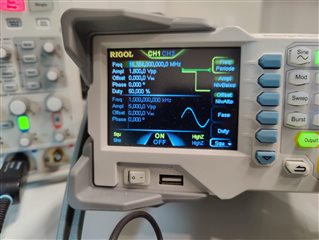

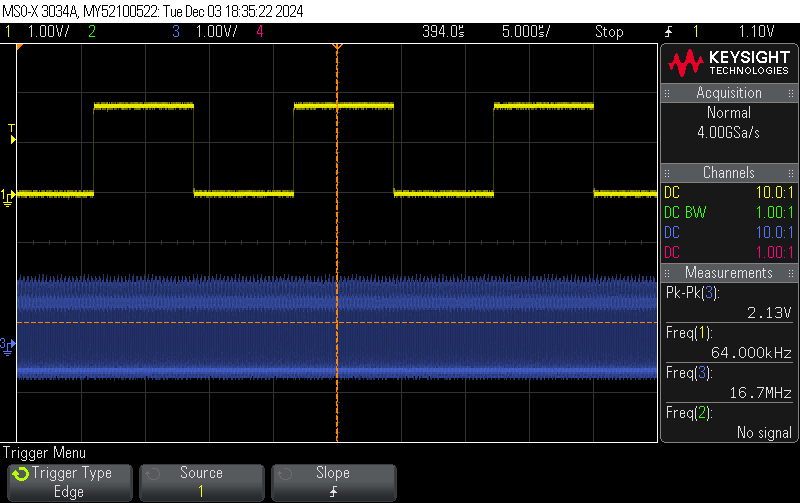

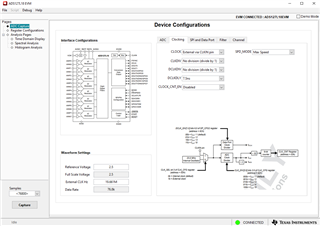

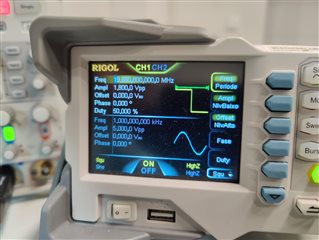

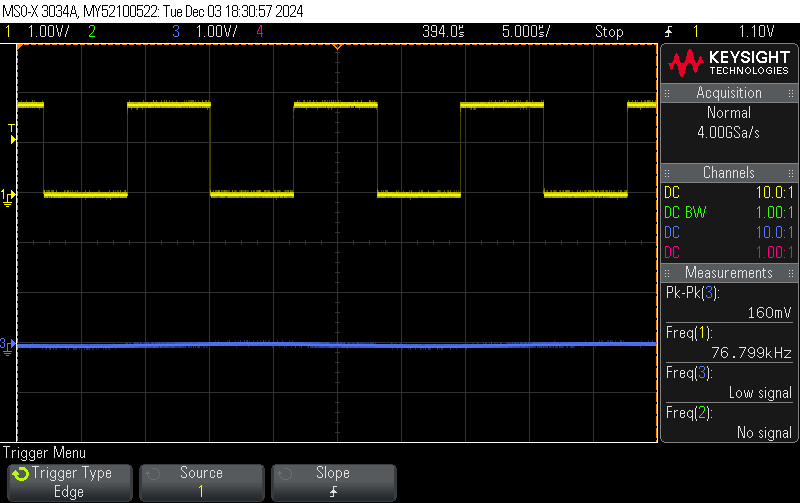

我正在使用 PHI 控制器板和独立硬件编程对 ADS127L18EVM 板进行实验、但我对数据速率存在问题。 使用外部发生器生成我的应用所需的两个频率16.384MHz 和19.6608MHz、对于分别为64KHz 和76.8KHz 的输出数据速率、器件的性能不同。 当我将频率设置为19.6608MHz 并将滤波器设置为宽带(OSR=128)时、通过探测 J3接头中 的 FSYNC 引脚、我可以获得预期为76.8KHz 的 FSYNC、但将发生器频率设置为16.384MHz 时、我可以获得频率为95KHz 至125KHz 的 FSYNC、而不改变任何设置。 我还使用 OSR= 128时的 SINC 滤波器进行了测试并获得同样的奇怪结果。 不过、我偶然发现、当将另一个探针从示波器连接到 ADC 的 CLKIN 引脚时、为了检查输入 CLK 频率、我现在可以获得正确的64KHz。 我用不同的示波器测试了这个并得到了相同的结果。 我还使用 EVM 上的32.768MHz 晶体对其进行了测试、滤波器设置为宽带、OSR=128且 CLKDIV=2、以获得64KHz 的数据速率、并且它按预期工作、我获得了64KHz FSYNC 信号、它在探测 CLKIN 引脚方面没有区别。

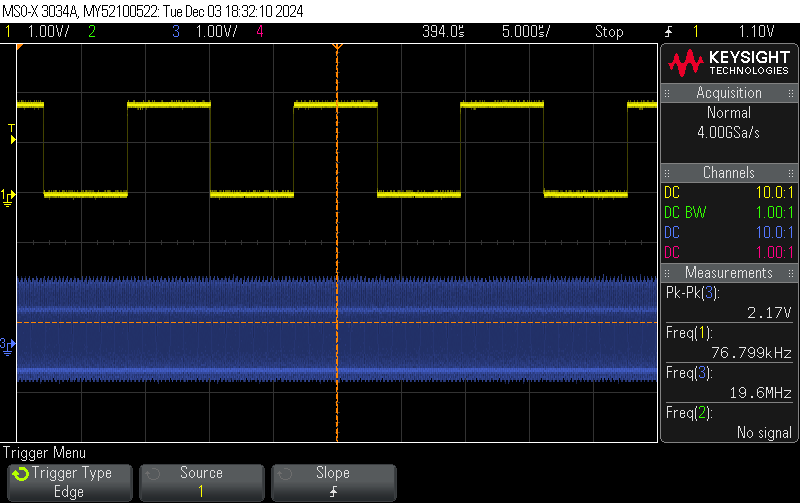

我将附上 EVM 软件、信号生成器和示波器上的一些图片:

如您所见、在64KHz 下探测和不探测 CLKIN 引脚时有不同的行为。

如您所见、探测和不探测 CLKIN 引脚的76.8KHz 时、行为没有变化。

您能帮助我们找出问题吗?