Thread 中讨论的其他器件:DAC38RF82

工具与软件:

您好!

我已经创建以下设置、以便从 Kintex UltraScale FPGA 驱动 DAC38RF82的时钟。

外部时钟50MHz 被馈送到 FPGA、以创建 DACClk 的200MHz 时钟基准。

在200MHz 中、我使用内部 DAC PLL 创建6600MHz 采样时钟、并将分频参考版本从 DAC 输出到550MHz 参考时钟(还使用外部分频器实现6600/12=550)。

然后、将550MHz 馈送到 TI-JESD204内核的 MGT 时钟基准。

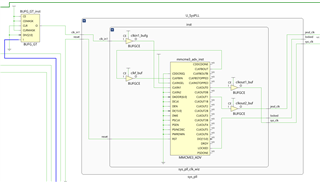

然后、我使用 mgt_tx_userclk2 (68.75MHz)输入 MMCM PLL 并为我的逻辑生成275MHz、同时使用一个68.75 MHz 副本作为 JESD204内核的 tx_sys_clock。 请参阅下图。

JESD204内核的文档表明、mt_tx_userclk2不需要 BUFG、因为它包含在内核中。

在符合 Vivado 实施要求时、我明确使用 BUFG_GT 驱动 PLL。

Vivado 实施继续失败、并显示以下消息:

[DRC REQP-123] CONNECTS_CLKINSEL_VCC_CONNECTS_CLKIN1_ACTIVE:u_SysPLL/inst/mmcme3_adv_inst:CLKINSEL 连接为高电平时的 MMCME3_ADV 需要 CLKIN1引脚处于活动状态。

问题:

1.提供的时钟方案是否可以接受?

2.在内部从 mgt_tx_usrclk2驱动一个 PLL 时是否出现问题?

3.如果是问题,我可以将信号路由到一个引脚,并提供给 PLL 输入时钟从外部引脚相同的信号?

4.是否有任何原因表明 Mgt_tx_usrclk2具有来自 MMCM 的不可接受的抖动?

谢谢!

Ilias