工具与软件:

尊敬的 Bryan

我很抱歉。 我回答你太晚了

已经是2个月了

您在结束时请求了波形

由于个人原因、我无法立即进行。

您是否还记得我不知道、但我现在将提供波形。

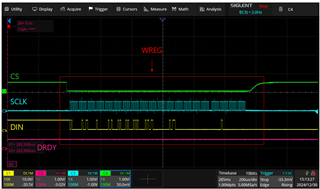

DRDY 看起来运行不稳定、

我想这就是我不执行转换的原因。

请检查问题是什么。

寄存器设置

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Kim Junsu:

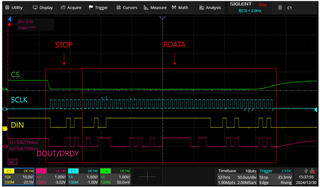

我不确定我是否了解您的问题? 您说 DRDY 的行为不准确、但我在示波器快照中仅看到1次 DRDY 转换。 您能否清楚地解释/说明问题所在? 您还在旧帖子中说 DOUT 始终为0xFFF、但这不是您在示波器屏幕截图中显示的内容

请在读回数据时将 DIN 保持为低电平、而不是高电平。 这显示在数据表中(见下文)

我也不清楚为什么要发送48个 SCLK 来读取数据。 如果 SYS 寄存器是默认值、则会禁用状态和 CRC、因此应只需发送32个 SCLK (RDATA 命令为8个、数据为24个)

-Bryan

尊敬的 Bryan:

我已经解决了之前有关发送48个 SCLK 的问题。 我修改了代码、以确保在使用 RDATA 时仅发送32个 SCLK、包括命令。

不过、我目前正面临一个新的问题。 来自 ADC 芯片的 DOUT 信号显示了一个波形、但 MICOM 读取的 MISO 始终为高电平。 我认为此问题可能与电路设计有关。 我们使用了三个 ADC (ADS124S08)和两个隔离器(ISO7731DWR)。 MOSI 和 MISO 信号通过隔离器传输到 MICOM。

从 ADC 进入隔离器的值正常工作、高电平为5V、低电平为0V。 但是、从隔离器到多元文化网的值在5V 时显示为高电平、在2.5V 时显示为低电平、如下图中的绿色波形所示。 因此、多元文化组织无法读取到低位。

根据数据表、DOUT 低电平有效、因此在正常状态下显示为高电平。 似乎最终连接了 ADC1_MISO 和 ADC3_MISO、在与 ADC1通信时、ADC3_MISO 保持高电平、这可能会导致此问题。

在下图所示的电路中、是否有办法以编程方式解决此问题? 例如、是否有寄存器可以将 DOUT 值更改为高电平有效?

请确认此问题是否只能通过修改电路来解决。

谢谢你。

尊敬的 Kim Junsu:

您在数据表的引脚功能表中引用了术语"低电平有效"。 此术语("低电平有效")与 DOUT/DRDY 引脚组合的 DRDY 功能相关。 换句话说、DRDY 上的低电平信号表示新数据可供回读。 组合 DOUT/DRDY 引脚遵循专用 DRDY 引脚的行为(假设 CS 处于低电平)

由于两个 DOUT 引脚连接在一起(ADC1和 ADC3)、两个 ADC 之间是否存在争用? 是否正确控制了每个 ADC 的 CS 线路、以便一次只从一个 ADC 读回数据? 当 CS 为高电平时、DOUT 引脚应为高阻抗;因此、CS 为低电平时的 ADC 应能够将线路驱动为高电平或低电平。

-Bryan