主题中讨论的其他器件: AFE58JD48

工具与软件:

你(们)好

我正与 AFE58JD48EVM 评估板合作、通过 JESD204B 接口将 ADC 数据发送到 FPGA、然后通过 Wavevision 在 JESD204B RX 上绘制提取的数据。

我将在信号发生器的 ADC 输入端发送一个1MHz 400mVpp 正弦波。

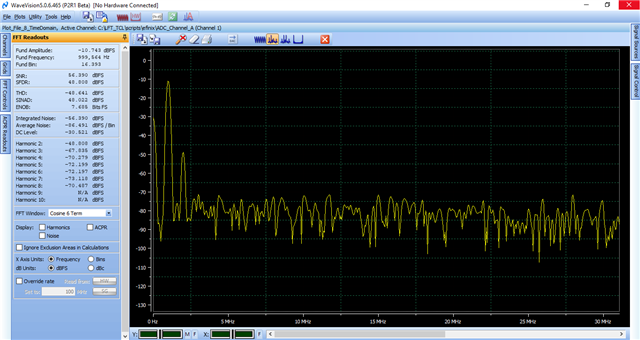

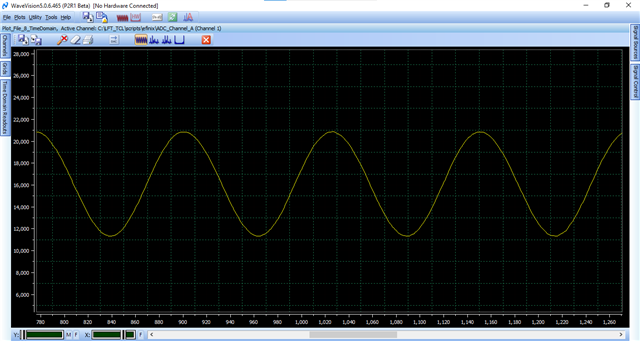

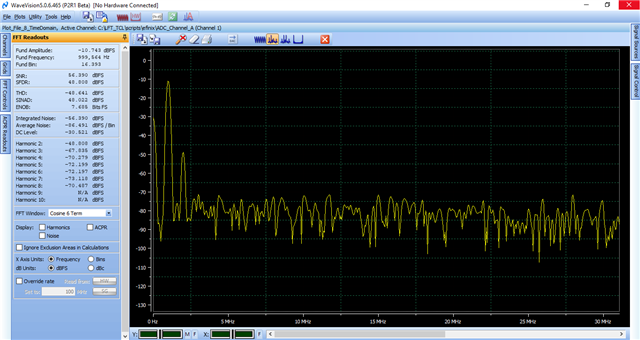

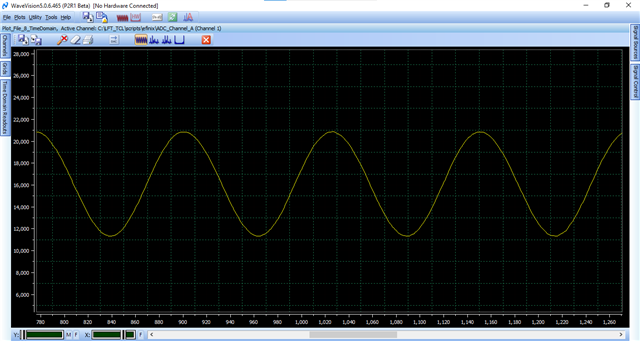

JESD204B RX 的绘制波形是一个正弦波、在1MHz 频率下具有正确的峰值、但也有谐波和高峰值。 我不知道有什么原因是相同的,所以可以有人帮助我这.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

你(们)好

我正与 AFE58JD48EVM 评估板合作、通过 JESD204B 接口将 ADC 数据发送到 FPGA、然后通过 Wavevision 在 JESD204B RX 上绘制提取的数据。

我将在信号发生器的 ADC 输入端发送一个1MHz 400mVpp 正弦波。

JESD204B RX 的绘制波形是一个正弦波、在1MHz 频率下具有正确的峰值、但也有谐波和高峰值。 我不知道有什么原因是相同的,所以可以有人帮助我这.