主题中讨论的其他器件:OPA192、

工具与软件:

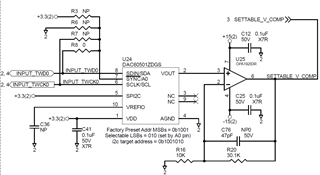

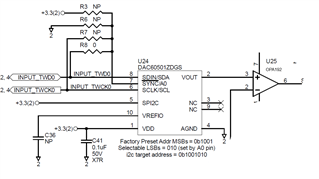

我们推出了一款新的 PCB、其中集成了 DAC60501ZDGS、根据数据表、DAC60501ZDGS 应在零 V out 时上电。

您可以看到、我们正尝试通过3.3V 的电压来运行 DAC。 另外、您将看到我们正在尝试在 i2c 模式下运行。 对于 i2c 地址、我们需要0x02 (010)、因此我们已将 A0绑定到 i2c 数据线。

在我尝试写入/读取命令寄存器之前、上电时、我观察到 Vout 大约为+830mV。 更令人担忧的是、我观察的是 VREFIO 读数大约为3.23V。 如果我理解了数据表和芯片的上电状态、VREFIO 应该是输出、而且我应该看到内部2.5V 信号存在。

假设我们在做一些奇怪的事情、我们用白色将3.3(2)的轨道连接到第二块板上的5(2)。 在这样做时、VREFIO 测量到2.5V 死区电压、值得注意。 但是、Vout 的测量值不是零、即+908mV。

3.3V 测量是在一个 PCB 上进行的、5V 配置是在第二个 PCB 上完成的。 我有2个包含 DAC60501的电路板、出现了此问题。 此外、我以5V 配置提升了 OPA192上的引脚以确保 DAC60501空载、但仍然出现此行为。

芯片上的器件标识如下:

TI27

P30RA

651Z

我尝试通过 i2c 进行通信、得到的效果似乎不错。 我可以写入寄存器并读回。 我知道我实际上在和芯片交谈、由于我在 i2c 总线上看到的 ACK、而且当我读取 DevID 寄存器时、非保留分辨率和 RSTSEL 位已进行适当设置。 我还可以写入 DAC 代码寄存器并读回值。 不过、Vout 保持在上述电压。 上电后、我已经尝试通过触发器寄存器发出软复位、但没有效果。 我已经试验了在写入一个新的 DAC 代码后改变 DAC 同步 EN 位和写入 LDAC 位、全部都没有效果。

我的5V 和3.3V 电压轨似乎在大约1ms 后出现。

我在这里有一点小损失、希望能够深入了解这款芯片可能会发生什么情况。 我不知道 Vout 应该是零、 我似乎从使用 i2c 命令的芯片获得的唯一响应是、当我在 config 中设置 REF_PWDWN 位时、我看到 VREFIO 行变为零。 但是、当我将 DAC_PWDWN 位设置为1时、输出仍然"停留"、以及我前面提到过的电压。

感谢你的帮助。