Other Parts Discussed in Thread: ADS7865

工具与软件:

您好!

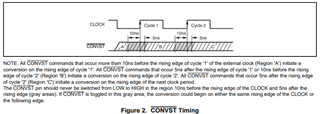

我想提出一个有关 ADS7865 ADC 时序规格的问题、特别是数据表第7页"图1"中提到的"T2"参数(忙线上升延迟)。 接口时序图"。

数据表指定了 T2的最小值为3ns、但未列出最大值。 您能否确认 T2的最大值?

为提供一些背景信息、我们正在设计一个 FPGA 来连接 ADS7865以检索 ADC 值。 我们的当前设计在 CONVST 输出后经过一段特定的延迟后从 ADC 读取数据。 由于 T4指定了从 BUSY 的上升沿到 RD 的下降沿的时序、因此即使在 t2的最大延迟情况下、我们也需要确认当前设计是否满足 t4。

谢谢!

Conor