Other Parts Discussed in Thread: DAC38J84, DAC38J84EVM, LMK04828

主题中讨论的其他器件:DAC38J84、、 LMK04828

工具与软件:

您好!

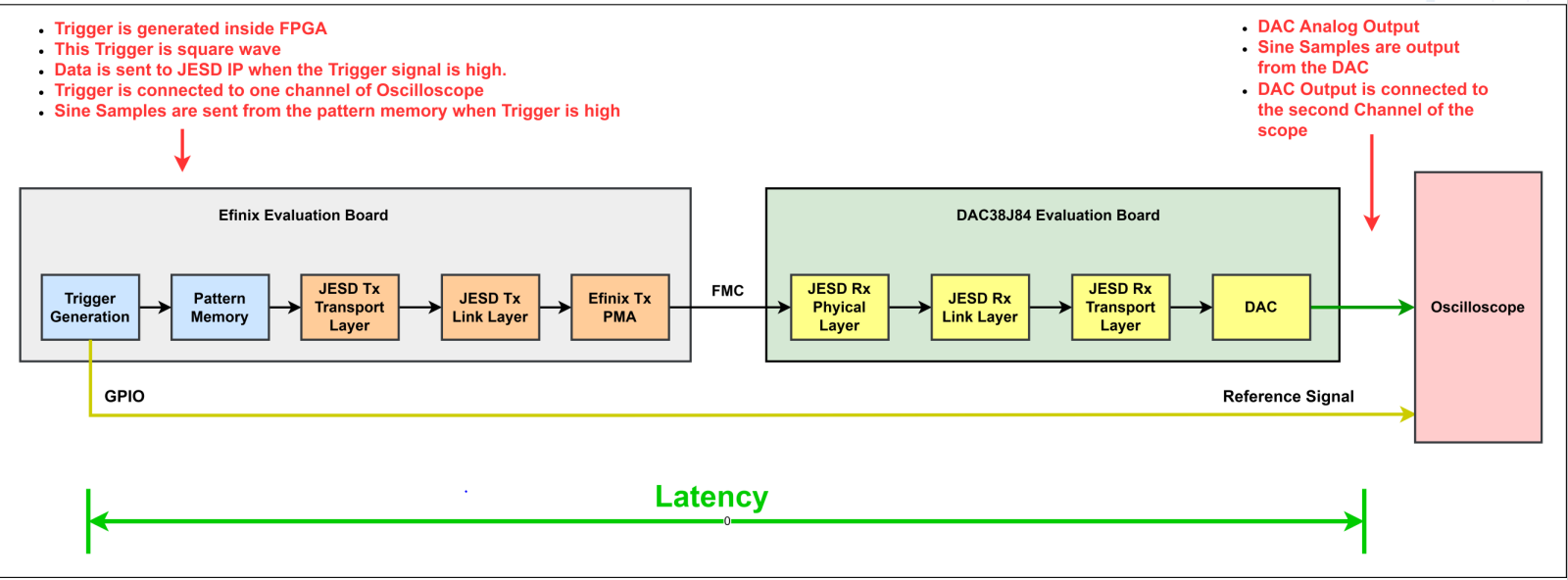

我们正在尝试使用 Efinix Titanium FPGA (Ti375N1156)和 DAC38J84 EVM 来确保 JESD204B TX IP 在子类1模式下的确定性延迟。 DAC38J84EVM 上的 LMK04828用于生成 DAC 和 FPGA 所需的时钟和 Sysref。 配置如下:

LMF = 442、K = 32、插值= x4

数据速率= 5Gbps、fpga_clk = 125 MHz、dac_clk = 250 MHz、Sysref = 3.90625 MHz。

RBD = 15

下面是参考设置图、用于使用上述设置实现确定性延迟。

- 触发脉冲以固定的间隔生成,提供给两条路径,一条进入模式存储器,在触发脉冲的每个上升沿开始将样本发送到 JESD204B TX IP,并在脉冲变为低电平时停止发送。 第二条路径指向 DAC38J84EVM 接头、通过该接头可在示波器上探测它以及 DAC 输出。

- 每个下电上电后、FPGA 评估板上的 JESD204C TX IP 与 DAC38J84 EVM 上的 JESD204B Rx IP 之间的链路序列将运行。 建立链路(JESD204B 达到 Data Phase)后、以固定宽度和脉冲间隙开始触发脉冲。 使用 SMA 电缆在示波器上探测 DAC 输出和触发器。

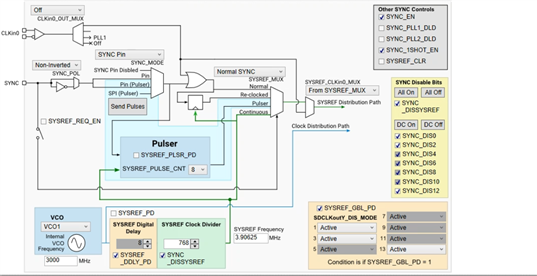

- LMK04828会在脉冲模式下生成 Sysref、并且所有时钟和 Sysref 分频器均会使用同步切换进行复位。 下面是所用配置的 GUI 快照。

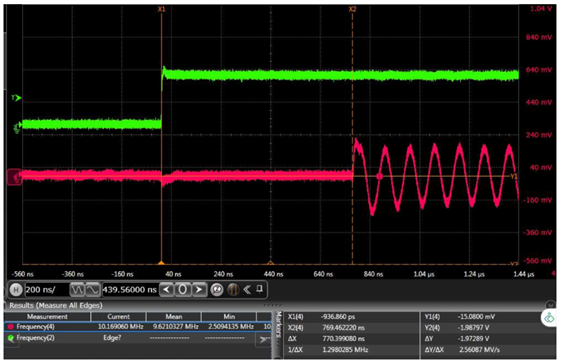

- 以下随附的图提供了示波器显示屏的一瞥。 绿色波形表示触发脉冲的上升沿、粉色波形表示 DAC 模拟输出、两者之间的延迟约为770ns。

- 总共执行了20次下电上电和链路序列的迭代、以检查确定性延迟。 触发器上升沿与输出波形之间的值在典型值770.738ns (最大值= 771.22ns、最小值= 769.62ns)附近有1.6ns 的不确定性。

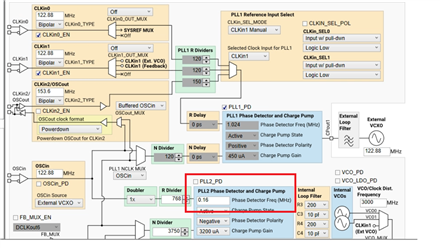

此外、我们将 在我们使用的 PLL 中使用160 kHz 的相位检测器频率、如下所示。

因此、我们将提出以下几点意见:

1) 1)为什么在典型值附近有1.6ns 的延迟?

2)相位检测器频率的低值是否导致产生的时钟中的抖动,从而导致这种变化?

2)如何尽量减少价值?