工具与软件:

大家好!

我对不同时钟频率下的部件功耗有疑问。 数据表中详细介绍了功耗、请参阅 fclk 的27MHz。 我计划在较低的频率下运行 ADC。 是否有任何关于功耗与 fclk 的可用数据? 我可以应用任何公式吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好!

我对不同时钟频率下的部件功耗有疑问。 数据表中详细介绍了功耗、请参阅 fclk 的27MHz。 我计划在较低的频率下运行 ADC。 是否有任何关于功耗与 fclk 的可用数据? 我可以应用任何公式吗?

您好、Raul、

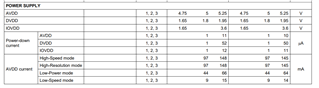

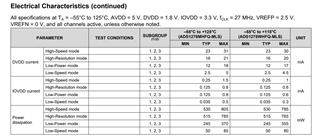

如产品说明书所述、整体功耗降低最大的是使用不同的工作模式、其中高速模式是最高的功耗模式、低速模式是最低的功耗模式。

但是、作为不同时钟频率下的估算值、DVDD 电流的100%将随时钟频率而变化、AVDD 电流的15%将随之变化。 IOVDD 的变化很小、可以在给定模式下估算为常数。

例如、上述电流数字是基于27MHz 的。 如果在高速模式下使用 f-clk=DVDD、可以预期典型的20MHz 17mA 电流将从27MHz 93mA 的23mA 降低到23*20/27=AVDD、并从97mA 降低到0.85*97+0.15*97*20/27=AVDD。

此致、

Keith Nicholas

精密 ADC 应用