Other Parts Discussed in Thread: LMK04826, AFE58JD48

主题中讨论的其他器件:LMK04826、 AFE58JD48

工具与软件:

您好!

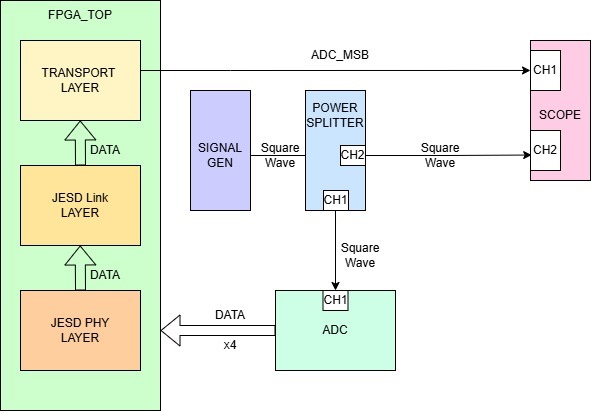

我们计划检查 JESD204B RX 和 ADC 之间的确定性延迟、我将使用一个参考设置图像来证明确定性延迟。

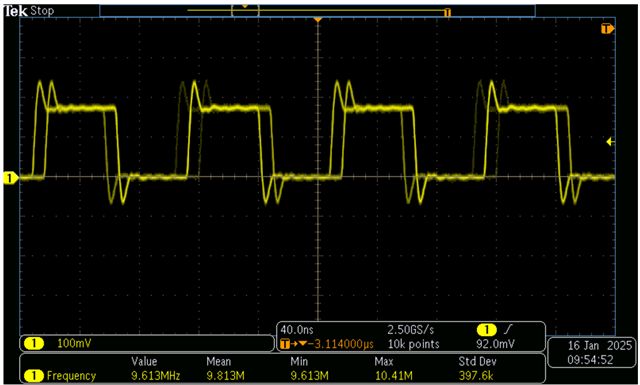

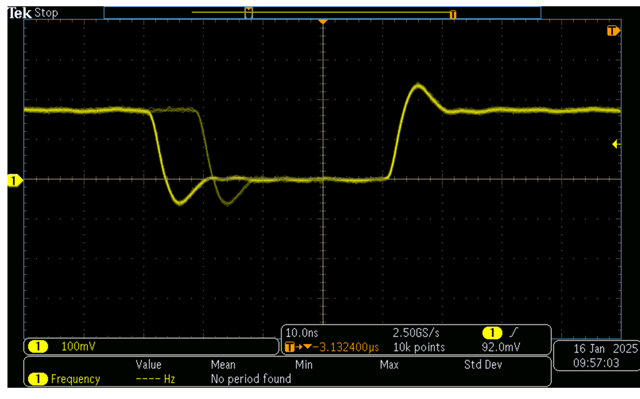

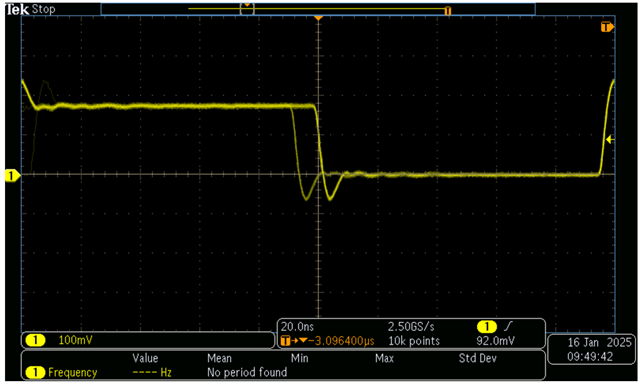

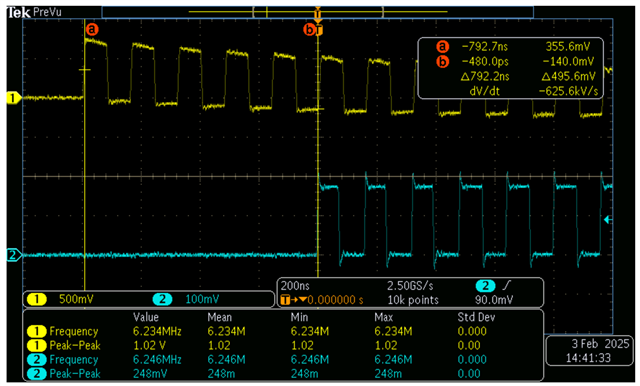

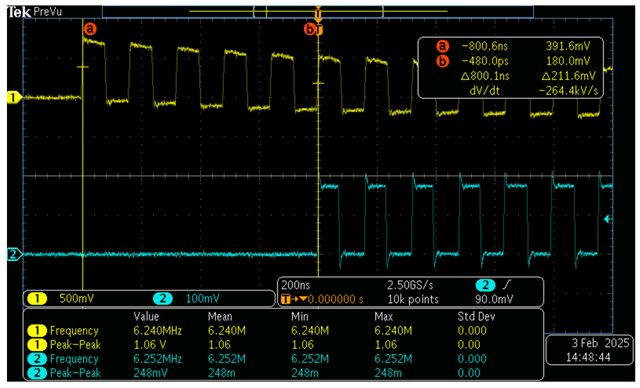

但 ADC 采样 MSB 位存在一些问题、如果我们捕获 ADC_MSB 位、则占空比不总是恒定的、并且上升沿和下降沿也有一些重叠。

我们将以不同频率发送正弦波作为输入以进行测试、但随着我们增加频率、重叠增加。 因此可以帮助我们调试该问题、因为如果占空比不是恒定的、我们就不能说信号是可重复的、以便用于证明确定性延迟。 我已经在5MHz 中附加了捕获图像。

5MHz