Other Parts Discussed in Thread: ADS1278EVM-PDK, ADS1278, ADS1278-SP, MSP430FR5969

主题中讨论的其他器件: ADS1278、 ADS1278-SP、 MSP430FR5969

工具与软件:

大家好!

我正在使用 ADS1278EVM-PDK 评估板对 ADS1278-SP ADC 芯片的数据子系统进行原型设计。 对于我们的数据系统、我们计划使用帧同步协议将 ADS1278芯片与 FPGA 板连接、因为这种方法可提供确定性状态机、这一点尤其重要、因为我打算在每次采样后切换外部模拟输入。

最初、我使用 ADS1278 GUI 通过 PHI 控制器控制 EVM、并使用示波器控制捕获的信号(DOUT1、SCLK、FSYNC、CLK)、以验证时序图并根据数据表确认我的理解。

接下来、我计划使用我自己的 FPGA 设计来连接 EVM、而不使用 PHI 控制器。 在继续之前、我非常感谢 TI 工程师和社区就我的下面概述的硬件和配置设置提供反馈。

硬件系统 :

由于可用 I/O 受限、我将仅使用八个通道中的一个。 外部模拟多路复用器(MUX)最终将切换输入信号。 目前、我在初始测试中使用稳定的1.5V 直流信号。

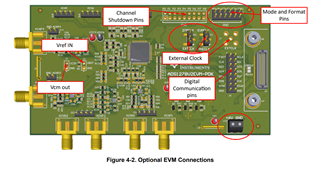

1. 从 EVM 上断开 PHI 控制器连接器。

2. 将引脚接头焊接到未使用的 PWDN 引脚上、并使用跳线禁用未使用的通道(相应的 PCB 孔未安装)。

3. 根据我的预期配置的指定、将配置引脚连接至 GND 或3.3V。

4. 使用板载振荡器 OSC_Y1选择 EVMCLK

5. 使用 EVM 提供的6V 电源连接器供电。

配置:

-

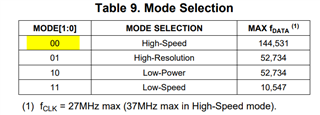

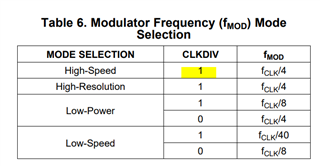

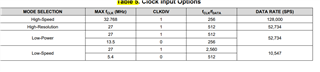

模式:高速(最初使用板载27 MHz 振荡器;如果需要、我们可以稍后将 Fclk 最大化)。

-

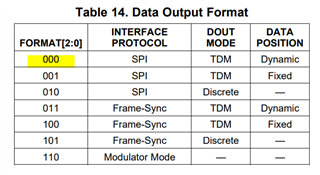

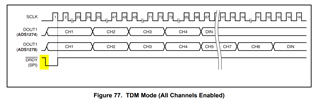

帧同步、TDM、动态模式(活动通道为 PWDN = 1、未使用通道为0)。

-

CLK_DIV 设置为1。

-

测试模式已禁用。

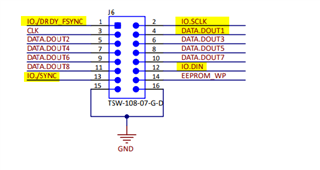

I/O

-

SYNC:同步(初始复位)

-

用于帧同步通信的 FSYNC、DOUT1、CLK、SCLK

-

CLK 与 SCLK 之比= 1

FPGA 逻辑 :

1. 将 SYNC 拉至低电平并保持至少一个 CLK 周期(当前使用两个周期)。

2. 生成128个 FSYNC 周期(每个 FSYNC 周期包含256个 CLK 周期、50%占空比)以准备数据转换。

3. 在下一个 FSYNC 周期开始时开始读取数据。 在 SCLK 的上升沿对数据进行采样、因为数据在下降沿移出。

**问题:

-

我的硬件和 FPGA 设置是否显示正确?

-

FPGA 电路板和 ADS1278EVM-PDK 之间建议的电源定序是什么? FPGA 板应该先通电、反之亦然? 如果必须先为 FPGA 供电、我将添加逻辑以防止自动 FSM 启动。

-

每次采样后切换模拟输入时、我是否必须使 SYNC 信号生效、然后再等待128个 FSYNC 周期? 我必须切换输入信号、因为所有输入信号都表示不同的科学数据。

-

连接 ADS1278-SP 芯片是否需要 FPGA?TI MSP430FR5969等 MCU 能否实现相同的性能? 鉴于任务主处理器上的引脚有限、欢迎提出任何替代接口方法的建议。

提前感谢您的指导和反馈!