Other Parts Discussed in Thread: ADS127L01

工具与软件:

您好!

我已经创建了一个在以下电路中使用 ADS127L0的电路板:

请注意、此电路之前存在问题、因为我遗漏了从引脚6到 VCC 以及从引脚28到 VCC 的连接以保持启用。 我已通过手动方式更正了此问题、但未反映在原理图中。

至于具体细节、请注意、该芯片与 AVDD/DVDD 和 AGND/DGND 共享公共 VCC 和 GND。 滤波器和 OSR 引脚的设置方式使其以低延迟/2048x 过采样运行。 这是因为当我有不同的滤波器和 OSR 设置时、我将要介绍的问题会变得更糟。

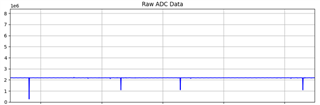

基本上、当我绘制来自 ADC 的数据时、在应该是常量时偶尔会出现尖峰:

请注意、我将从这里的 ADC 绘制原始值。

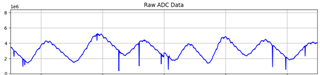

另一个示例:

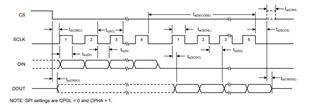

我已确保进入正确的 SPI 模式、并在轮询数据之前等待 DRDY 引脚变为低电平。 对于较低的 OSR 或不同的滤波器、或者如果我在代码中的主循环中降低延迟、此问题会变得明显更糟(每100个样本有更多的尖峰)。

因此、这使我相信这是与时序相关的问题、但根据数据表、我将使用完全处于3V 电源可接受值范围内的2MHz SPI 时钟、并且我将使用正确的 SPI 模式。 我正在等待 DRDY 输出变为低电平、然后再进行测量、我将环路延迟1ms。

这是否可能是时间问题? 如果是、如何解决? 或者我在焊接时是否以某种方式损坏了我的 ADC (请注意、我有两个表现出相同行为)

谢谢!