Other Parts Discussed in Thread: ADC3663, SN65LVDS100

主题中讨论的其他器件: SN65LVDS100

工具与软件:

大家好、团队成员:

客户正在使用连接 Xilinx 7035的 ADC3663进行测试。

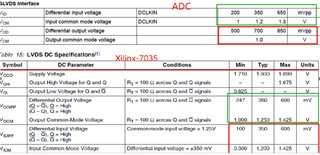

他们正在考虑 ADC3663数据表和 FPGA 数据表之间有关 SLVDS 和 LVDS 的不同电压标准

我看到了一些关于信号标准的 E2E 问题、但我不确定我们是否需要转换器、或者我们是否可以直接连接 ADC3663和 FPGA。

- DCLKIN 使用

FPGA 可以输出具有1至1.425V VCM (典型值为1.2V)和247至600mV (典型值为350mV)的信号 VOD 至 ADC3663

ADC3663输入规格为1-1.3V (典型值为1.2V)和200至650mVpp (典型值为350mVpp) VOD

- 数据通道

ADC3663可在500至850mVpp VOD 范围内输出1.0Vcm。

FPGA 可以接收0.3-1.425V、典型值为1.2V、VOD 范围为100mV 至600mV

我的问题是:

如何理解 ADC3663中的输入 Vcm 和 VOD、这是否意味着我们可以接受1到1.3V 之间的任何 VCM 电压、并接受200到650mV 之间的 VOD 电压、ADC3663如何识别高电平和低电平信号?

ADC3663能否直接连接 FPGA? 或者我们需要一些交流耦合+偏置方法或转换器?

谢谢!

Yishan Chen