器件型号:ADC3644EVM

工具与软件:

尊敬的技术支持团队:

我安装了 HSDC v6.0、但它不包含 ADC3644。

如果我需要安装补丁、您可以提供吗?

此致、

TTD

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号:ADC3644EVM

工具与软件:

尊敬的技术支持团队:

我安装了 HSDC v6.0、但它不包含 ADC3644。

如果我需要安装补丁、您可以提供吗?

此致、

TTD

尊敬的 Rob:

感谢您的答复。

我的配置是 ADC3644EVM (ADC35XX GUI)+ TSW1400EVM (HSDC Pro v6.0)。

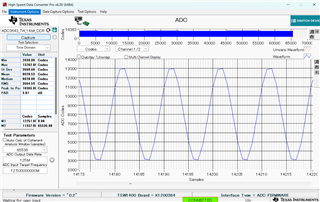

Anaglo 输入为12.5MHz、 采样时钟为125m、因此我得到了具有10个样本的正弦波(1个周期)。

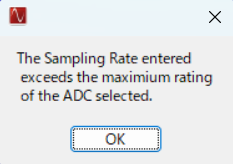

由于使用 ADC3643 ini 文件、我在 HSDC Pro 上为"ADC 输出数据速率"设置125m 时、忽略了以下消息。

问题1:

J1的最大模拟输入范围(dBm、Vpp)是多少?

ADC3644EVM 在 ADC 输入之前具有 THS4541集成变压器。

问题2:

如果125M 的评估正确、我要更改100MSPS。

根据用户指南、需要使用外部时钟(如果 CDC 生成100M、这是最佳解决方案、但不支持 GUI (CDC Disable))。

然后我的理解,我需要尝试根据"5外部时钟硬件设置"更改100MSPS 的硬件

是这样吗?

•DNI R32、R40⇒从 CDC 禁用内部 CLK

•安装 R36、R37 (0 Ω 电阻器)⇒启用来自 J8的外部时钟

•将采样时钟连接到 J8。 将 DCLKIN 连接到 J15。

•DNI R176⇒禁用 InternalDCLKIN_P

•将 C129替换为0 Ω 电阻器

最棒的餐厅

TTD

尊敬的 Rob:

感谢您的答复。

我 在检查 GUI 代码是否削波期间启动了小电平、最高达1Vpp (3.979dBm)。

这是我所附的图片。 我相信这是 Rev.F (DC104F)。

我在原理图中插入了注释、并使用了 SMA (J8)的外部采样时钟的 picutres。

由于 DDR CMOS 模式(非 CMOS 串行模式)、它观察到更改 DCLKIN 的 SMA (J13)周围的 C 和 R。

您能评论一下吗?

e2e.ti.com/.../ADC3644EVM_5F00_Rev.F.zip

我参考了随附的以下 E2E 原理图。

e2e.ti.com/.../OutputFiles.zip

ADC3644EVM:原理图和光绘数据-数据转换器论坛-数据转换器- TI E2E 支持论坛

此致、

TTD