主题中讨论的其他器件: DLPDLCR3310EVM

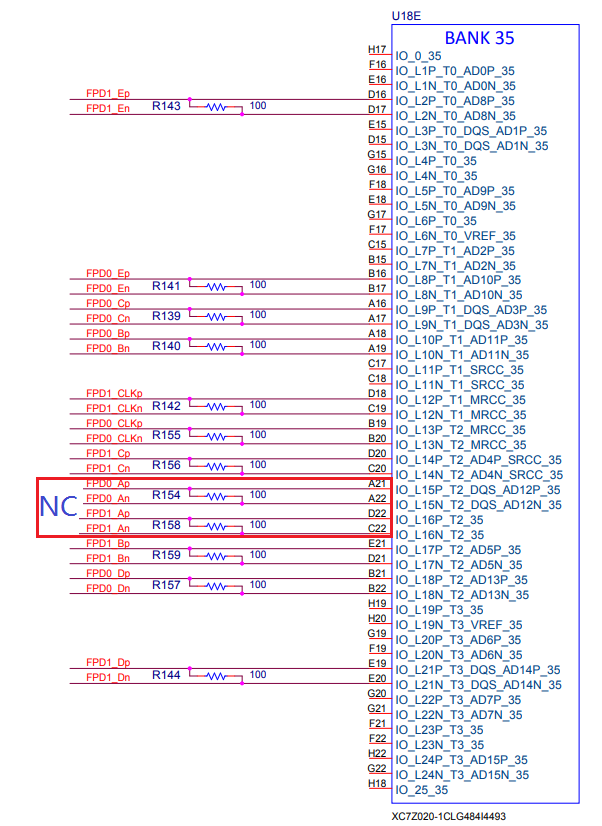

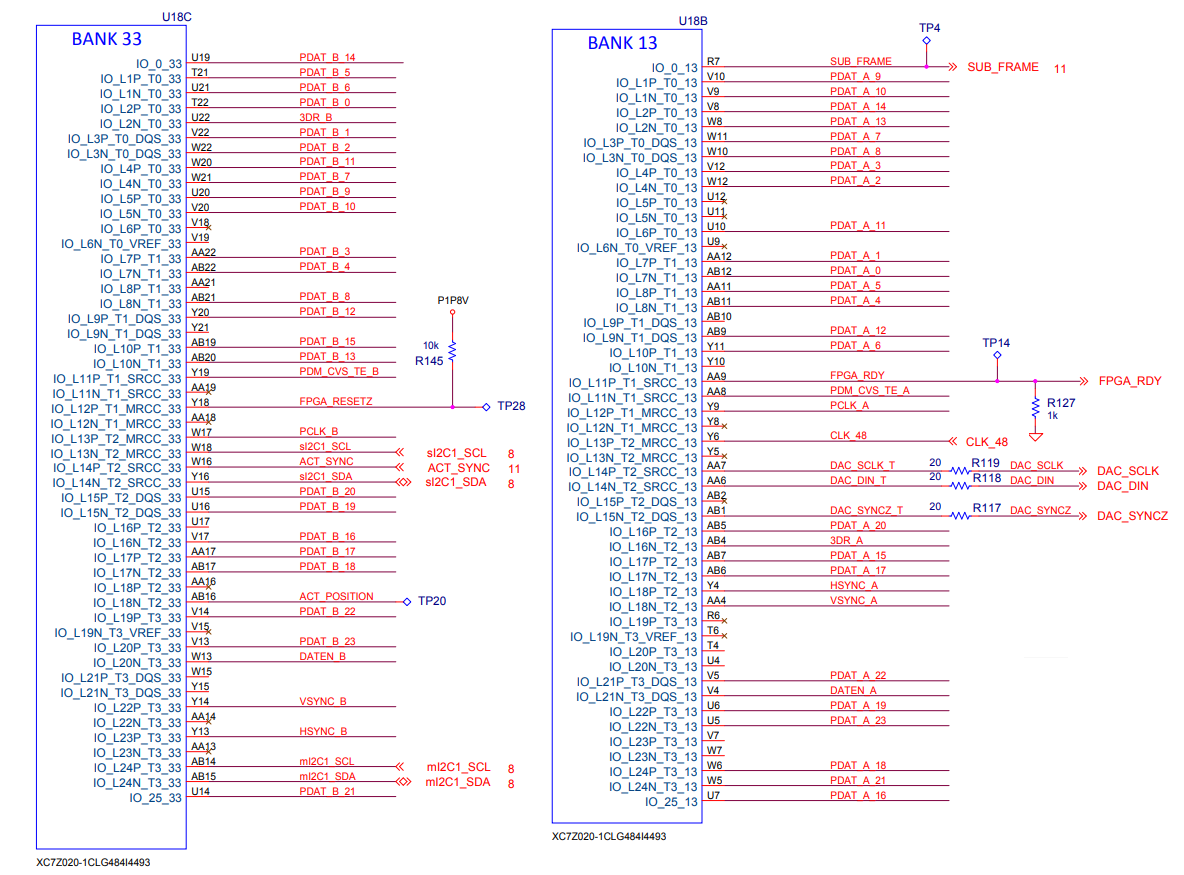

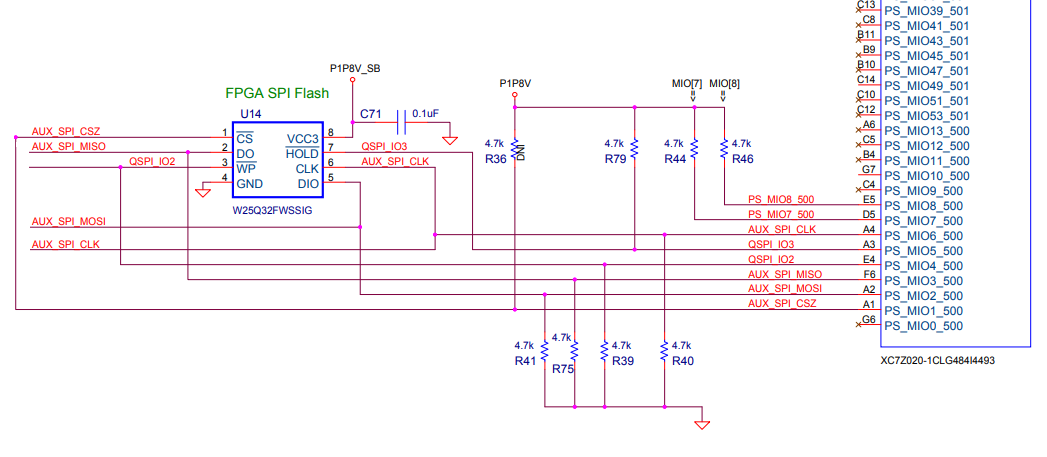

FPGA 模型:XC7Z020-1CLG484I4493

DDR3型号:MT41K64M16TW-107:J

DLPC 型号:dlpc3437

根据 TI 提供的0.33公板 DLPDLCR3310EVM 显示板电缆、FPGA 的视频输入使用 GM8775C 将 MIPI 转换为双8位 LVDS 以驱动 FPGA、从而离开每组中最低的位:FPGA_ AP/AN 和 FPD0_ AP/AN、如下图所示

与公共版本一样、我们还使用外部 SPI、

请提供相应的 FPGA 软件(烧录 FPGA SPI 闪存的方法)