您好!

FPGA 是否具有检测易失性和非易失性存储器故障的监控策略?

和...

FPGA 是否启用读回 CRC 相关功能来检测 SEU?

此致、

Johns。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

FPGA 是否具有检测易失性和非易失性存储器故障的监控策略?

和...

FPGA 是否启用读回 CRC 相关功能来检测 SEU?

此致、

Johns。

您好、Johns、

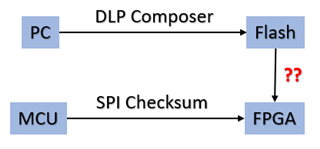

与其他 DLP DMD 控制器不同、FPGA 目前不执行任何类型的存储器 BIST。 因此、主机有责任从外部验证以易失性或非易失性形式存储器内容是否正确。 基于 FPGA 的 DGP 应用所需的所有存储器内容都驻留在单个 OSPI NOR 闪存中、并作为 DLP Composer 的单个.img 二进制文件加载。 DLP Composer 执行存储器擦除、存储器写入和存储器验证(快速读取)例程、这是闪存生产方法的推荐实现方案。 作为现场主机应用的一部分、主机控制器也可以执行对 OSPI NOR 闪存的快速读取、以确保与有效/原始二进制文件相比、FPGA 配置和视频位平面数据不会损坏。

根据 DLP3021-Q1 FPGA 用户指南、在 SPI 读取命令的末尾附加了一个校验和来检测传输期间的错误、这是唯一的内置回读验证形式。

您好、Akeem

感谢您的解释。

使用 DLP Composer 验证 PC 编程闪存的正确性。 ~确认

从 MSP430到 FPGA 的指令正确性由 SPI 的校验和验证。 ~确认

但是、FPGA 和闪存之间是否有任何检查机制?

2问题:

1. FPGA 加载程序后、它是否仍会以任何方式检查闪存?

损坏闪存本身? 视频数据的一致性? 视频 数据的准确性? 等等

2、FPGA 本身。 在 DLP3021或2021的 FPGA 版本中是否启用了 ECC 功能?

此致、

Johns。

您好、Johns、

回答您最近的两个问题:

1) 1) FPGA 加载程序后、无论如何都不会检查完整的闪存。 如果闪存损坏或八进制 SPI 总线信号完整性较差、FPGA 可能无法正确启动、或者视频播放失真。 对从闪存加载的序列信息进行错误检查、这样序列中的错误将设置 VCM_SEQABORT_ERR 状态位、指示发生了序列中止错误。

2) 2)没有迹象表明在设计适用于 DLP2021或 DLP3021 DMD 的 FPGA 固件时启用了 ECC。