This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

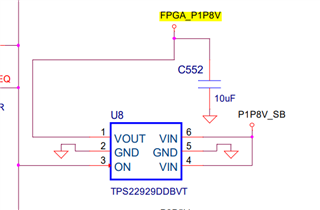

我的客户正在使用 DLPA2005开发 DLPC3436、上电时序要求在 FPGA_1.8V 之后复位应至少10ms。 数据表上的上电时序来自 DLPA3000、我对符合 DLPA3000时序要求的 DVH 板进行了测试。 但是、在我们使用 DLPA2005的 EVM 板上、延迟仅为大约2ms。 我的客户注意到了这一点、我们发现 TPS22929带来了大约6ms 的延迟(我们 EVM 上的设计相同)。 尽管我们移除了 TPS22929、但延迟仅为7ms 左右。 是否应严格遵守此时序要求?

Sophie、您好!

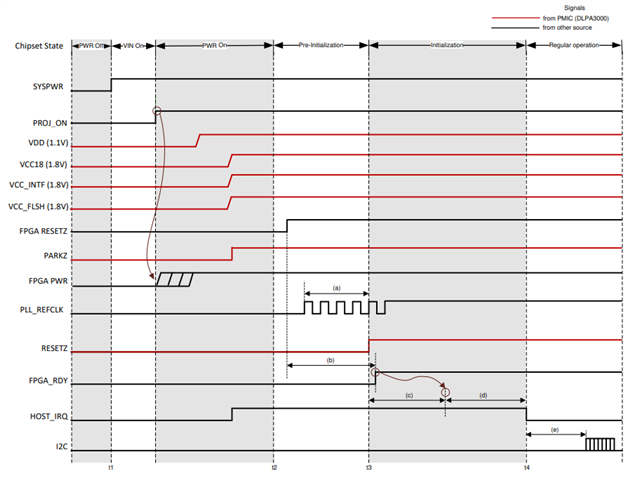

DLPC3436 上电时序图如下所示。 由于 FPGA 启动逻辑的原因、FPGA_RESETZ 和 FPGA_RDY 之间的时间是1.5s。 T3是 RESETZ 失效的点、指示控制器自动初始化例程开始。 为了确保正常运行、此图中的每个时序都应准确地反映在客户的系统中。

您在随附的图像中提到了哪个时序图、其中显示 RESETZ 和 FPGA_1.8V 之间的10ms 延迟? 在哪里可以找到该图?

此致!

麦克斯因

谢谢 Maxine。 我没有注意到数据表有一些更新。 这张图片来自旧版本、但现在无关紧要。

Sophie、您好!

不用客气。 很高兴我能提供帮助。

此致!

麦克斯因