主题中讨论的其他器件: DLPA2005、 DLPA3000

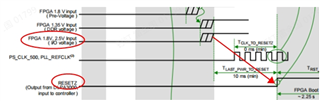

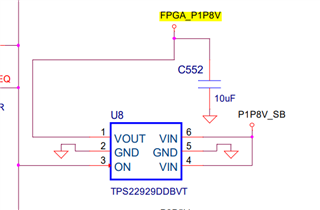

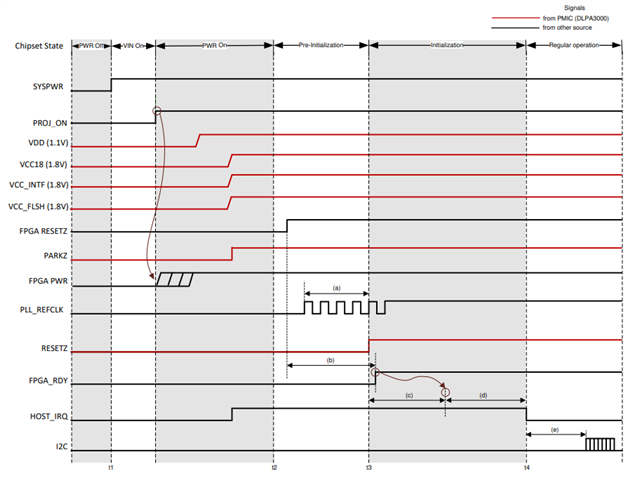

我的客户正在使用 DLPA2005开发 DLPC3436、上电时序要求在 FPGA_1.8V 之后复位应至少10ms。 数据表上的上电时序来自 DLPA3000、我对符合 DLPA3000时序要求的 DVH 板进行了测试。 但是、在我们使用 DLPA2005的 EVM 板上、延迟仅为大约2ms。 我的客户注意到了这一点、我们发现 TPS22929带来了大约6ms 的延迟(我们 EVM 上的设计相同)。 尽管我们移除了 TPS22929、但延迟仅为7ms 左右。 是否应严格遵守此时序要求?