主题中讨论的其他器件: DLPC3478、 DLPC3438和 DLPC3470

您好!

我们已测试 使用 DLPA2005的定制 DLP 控制器板。

在 EMI 暗室中进行 EMI 辐射预测试期间、我们发现 在 330 MHz 附近观察到一个超出建议限值的问题。

由于只有在打开投影仪时才会发生这种情况、因此我们可以得出结论认为这与投影仪相关的 IC、图形等相关: 例如 DLPC3478、DLPA2005

虽然我们能够通过适当屏蔽外壳来轻松解决问题、但 现在我们正在 优化电路设计、从而更好地提高 EMI 特性。

在 查看 IC 手册时、我们发现了一些有趣的部分:

DLPA2005数据表链接如下所示:

https://www.ti.com/lit/ds/symlink/dlpa2005.pdf?ts = 1692140216596

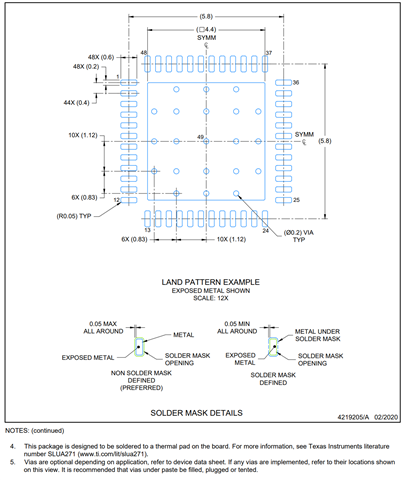

1.过孔样式(P54)

"根据应用可选通孔、请参阅器件数据表。 如果实施了任何通孔、请参见此视图中所示的通孔位置。 建议对焊锡膏下方的通孔进行填充、堵塞或包覆。"

我能不能问为什么要为这些过孔提供特定的栅格布局? 我认为其中肯定有原因、但 数据表中没有明确说明。

请注意、 评估板也 严格遵循此指南。

如果我们不遵循该指南、会发生什么情况?

2.布局指南(P44)

P44有一些指南、页面上特别强调了该指南的重要性、 即如果做法不当、EMI 会出现问题。

我们希望缩小部件范围、在近场探头测试期间、 我们发现、DMD FPCB、LED 电缆和 DLPC3478器件上的辐射更大、而不是来自 DLPA2005附近的区域。

这是否正常?

与使用 DLPC3478和 DLPA2005的定制设计板相关的 EMI 通用指南

是否有任何其他材料与特定器件的 EMI 防护设计相关?

(DLPC347x、DLPA2005等)

谢谢。