您好、TI 专家

由于 DLPC23x-Q1 ASIC 输入接口支持行业标准 OpenLDI (FPD-Link I)接口(Open

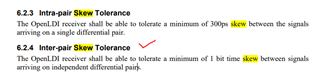

LVDS 显示接口规范 v0.95 - 1999年5月13日)和 v0.95规范中显示、接收器应能够承受独立差分对之间至少1位时间偏差。

您能解释一下如何在 IC 端实现此功能吗?

B·京城

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 专家

由于 DLPC23x-Q1 ASIC 输入接口支持行业标准 OpenLDI (FPD-Link I)接口(Open

LVDS 显示接口规范 v0.95 - 1999年5月13日)和 v0.95规范中显示、接收器应能够承受独立差分对之间至少1位时间偏差。

您能解释一下如何在 IC 端实现此功能吗?

B·京城

京城

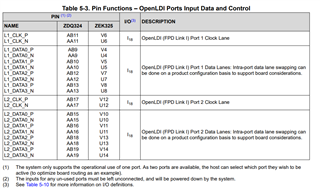

DLPC230不能同时支持双端口、并且该实现不支持单端口的1位偏移。 DLPC230被设计成具有用于两个端口的引脚。 请参阅数据表的第5-3节-注释1。

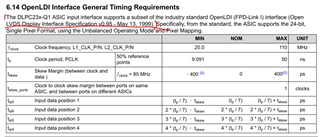

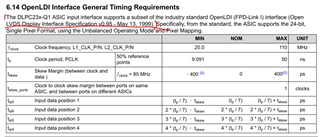

DLPC230确实支持端口之间的1位偏移。 但是、到目前为止、我们仅实现了在单个端口上支持高达110MHz 的像素时钟的系统。 可能、未来如果我们有需要更高分辨率的 DMD、则可以实现并提供双端口配置、在这种情况下、将支持每个端口之间的1位偏移。 从 DLPC230的 IC 输入、系统应设计为使用支持高达110MHz 的24位 RGB 数据的单个端口。 在这种情况下、单个端口的最大偏斜在数据表的第6.14节中定义为 Tsketch。 https://www.ti.com/lit/ds/symlink/dlpc230s-q1.pdf。 如果这能解决问题、请告诉我。 我还将通过另外几个开放线程来解决计时要求。

请告知我们、这是否解决了您的问题。