主题中讨论的其他器件:DLP9500、 DLP650LNIR、DLPA200

工具与软件:

您好、TI 专家:

我采用自己的电路板设计、硬件架构是 FPGA+DLPC410+DLP9500。

我们采用了一种新方法、将 TI 提供的固件刷写到闪存中。 目前、DDC_Version 返回0、而之前在使用 DLPR410A 时、DDC_Version 返回7。 我们不确定采用这种新方法时 DDC_Version 应该是什么、以及0与7之间的区别是什么。 是否有任何重要注意事项?

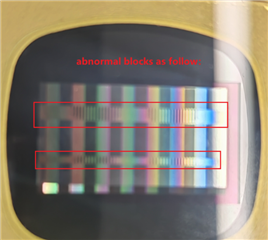

我们使用之前用于 DLPR410A 测试的相同代码在修改后的固件下测试了 PCB、并发现了以下问题:

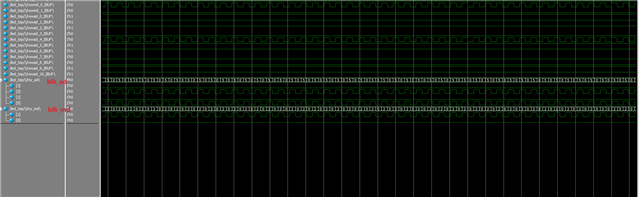

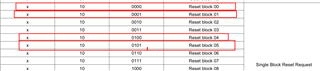

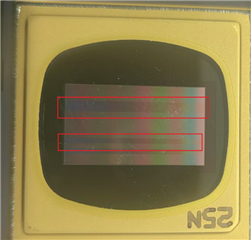

上电并完成初始化后、大约三个块出现故障、如 Picture1所示。 当在 DMD 上显示图像时、这些块的行为与预期不符、如 Picture2中所示。 我们监控了 rst_active 信号并观察到一个4.5 µs 脉冲、表示其运行正常。 但是、在切换图像时、这些块仍然无法响应。

将 pwr_float 信号设置为低电平并测量 PCB 上 DLPC410的 AC17引脚、将显示高电平信号。 在正常情况下、它应该处于悬空状态、但 DMD 没有变化。

您能否提供任何故障排除建议?

非常感谢!