工具与软件:

现在有 PCB、 现在可以显示 SN65DSI83的测试图形。

我现在将100MHz CLK 连接到 REF CLK 引脚、而没有 MIPI-DSI CLK、因为源器件尚未就绪。

我需要输出27MHz "LVDS"CLK。

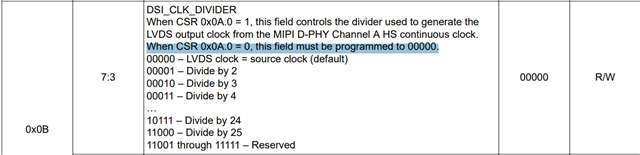

在数据表中 、我认识到这一点

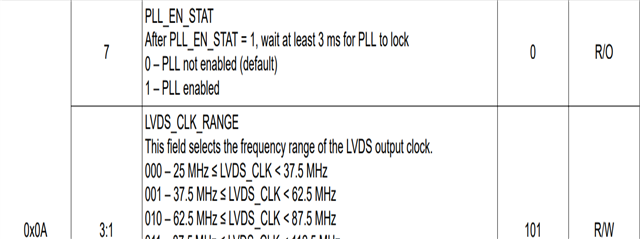

ADDR 0x0B 1:0位是用于将 FREQ 从 REFCLK 更改为 LVDS CLK 的设置

ADDR 0x0B 7:3位是用于将 FREQ 从 DSI CLK 更 改为 LVDS CLK 的设置。

执行场削弱

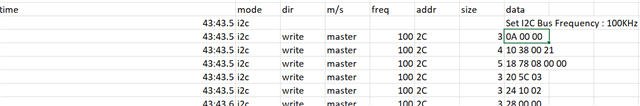

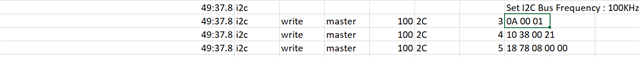

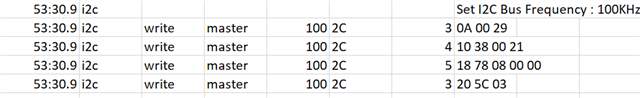

我设置0x0A =0x00 + 0x0B = 0x01、 下次我设置 0x0A =0x00 + 0x0B = 0x2A、

LVDS CLK 已更改!

为什么会发生这种情况?