您好!

我们目前正在使用 TCA9617B 进行设计、想就数据表中第7.2.1.2节详细设计过程、特别是关于台阶上冲的几点说明。 您能就以下问题提供您的见解吗?

问题1.

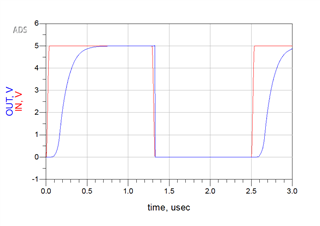

如果 B 侧的输入信号是占空比为50%的时钟、我认为基座过冲的增加可能会使 A 侧输出波形的占空比失真。 这种理解是否正确?

问题2.

为了防止发生基座过冲、应将 B 侧的输入信号四舍五入多少?

或者、是否有其他方法可以防止基座过冲?

问题3.

基座过冲是否会在正常运行中给 TCA9617B 带来问题?

问题4.

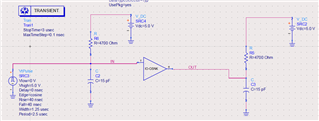

是否可以使用 TINA-TI 来执行 TCA9617B 的信号完整性仿真? 基座过冲是否可以重现?

如果是、您能提供一些基准数据吗?

问题5.

是否可以使用 TCA9617B 的 IBIS 模型与除 TINA-TI 之外的 SI 仿真器来执行信号完整性仿真?

在这样的仿真中可以再现台阶电平过冲吗?

谢谢!

Conor