Other Parts Discussed in Thread: TLK10232, TLK10232EVM

工具与软件:

关于 TLK10232的使用、我们还有几个问题。 它们是:

* REFCLK 连接

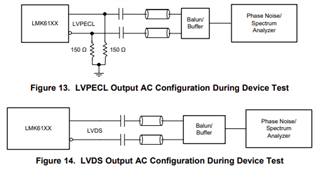

-当使用156.25MHz LVPECL 振荡器作为时钟源时、REFCLK 输入的端接要求是什么? 是否有可用的基准电路? EVM 原理图显示了从交流耦合电容器到 TLK 引脚的直接连接。

-上升/下降时间要求有多重要? 查找可以安全地保证满足最大值的 LVPECL/LVDS 振荡器似乎并不容易。 是否有关于振荡器的建议?

*附加文档

数据表中的表8-22"更多信息、请参阅 TLK10232启动过程(单独的文档)"。 我们如何访问这份单独的文档?

* XAUI 链接/桥接器并非没有错误

在 LS/XAUI 侧、TLK 器件在一个通道上连接到 NWP (MCHP)、在另一个通道上连接到10GPHY (MCHP)。 在一个场景中、我们已使用内部开关桥接2个通道(请参阅我的另一个 E2E 帖子)。 虽然此桥接器一般可以正常工作、但我们面临这样一个事实:两个 XAUI 链路伙伴(NWP、PHY)都报告非常少量的 FCS 错误。

必须注意的是、在此测试期间、没有任何东西连接到 HS/KR 侧。

XAUI 桥接器配置中0x1E 器件(特定于供应商)的寄存器转储如下所示(PHY 侧):

寄存器值说明

1Ex0000 0x0610 GLOBAL_CONTROL_1

1Ex0001 0x0b24 CHANNEL_CONTROL_1

1Ex0002 0x831d HS_SERDES_CONTROL_1

1Ex0003 0xa848 HS_SERDES_CONTROL_2

1Ex0004 0x1500 HS_SERDES_CONTROL_3

1Ex0005 0x2000 HS_SERDES_CONTROL_4

1Ex0006 0xf115 LS_SERDES_CONTROL_1

1Ex0007 0x0000 LS_SERDES_CONTROL_2

1Ex0008 0x0000 LS_SERDES_CONTROL_3

1Ex0009 0x0380 HS_OVERLAY_CONTROL

1Ex000A 0x1fff LS_overlay _CONTROL

1Ex000B 0x0d10 loopback_TP_CONTROL

1Ex000C 0x0371 LS_CONFIG_CONTROL

1Ex000D 0x2f80 CLK_CONTROL

1Ex000E 0x0000 RESET_CONTROL

1Ex000F 0x70af CHANNEL_STATUS_1

1Ex0010 0x0000 HS_ERROR_COUNTER

1Ex0011 0x0000 LS_LN0_ERROR_COUNTER

1Ex0012 0x0000 LS_LN1_ERROR_COUNTER

1Ex0013 0x0000 LS_LN2_ERROR_COUNTER

1Ex0014 0x0000 LS_LN3_ERROR_COUNTER

1Ex0015 0x4146 LS_STATUS_1 (lane0)

1Ex0015 0x4146 LS_STATUS_1 (lane1)

1Ex0015 0x4146 LS_STATUS_1 (lane2)

1Ex0015 0x4146 LS_STATUS_1 (lane3)

1Ex0016 0xf006 HS_STATUS_1

1Ex0017 0x2000 dst_control_1

1Ex0018 0x0c20 dst_control_2

1Ex0019 0x2500 DSR_CONTROL_1

1Ex001A 0xac20 dsr_control_2

1Ex001B 0x1043 DATA_SWITCH_STATUS

1Ex001C 0x0000 LS_CH_CONTROL_1

1Ex001D 0x0000 HS_CH_CONTROL_1

1Ex001E 0x0000 EXT_ADDRESS_CONTROL

1Ex001F 0x0000 EXT_ADDRESS_DATA

1Ex8003 0x0283 VS_10G_LN_ALIGN_ACODE_P

1Ex8004 0x017c VS_10G_LN_ALIGN_ACODE_N

1Ex8021 0x000f MC_AUTO_CONTROL

1Ex802A 0x02fd dst_on_char_control

1Ex802B 0x02fd dst_off_char_control

1Ex802C 0x0207 dst_stamp_char_control

1Ex802D 0x02fd DSR_ON_char_control

1Ex802E 0x02fd DSR_OFF_char_control

1Ex802F 0x0207 DSR_STUFF_CHAR_CONTROL

1Ex8040 0x0000 LATENCY_MEASE_CONTROL

1Ex8041 0x0000 LATENCY_COUNTER_2

1Ex8042 0x0000 LATENCY_COUNTER_1

1Ex8100 0x0000 TRIGGER_LOAD_CONTROL

1Ex8101 0x0000 TRIGGER_EN_CONTROL

XAUI 桥接器配置中0x1E 器件(特定于供应商)的寄存器转储如下所示(NWP 端):

寄存器值说明

1Ex0000 0x0610 GLOBAL_CONTROL_1

1Ex0001 0x0b24 CHANNEL_CONTROL_1

1Ex0002 0x831d HS_SERDES_CONTROL_1

1Ex0003 0xa848 HS_SERDES_CONTROL_2

1Ex0004 0x1500 HS_SERDES_CONTROL_3

1Ex0005 0x2000 HS_SERDES_CONTROL_4

1Ex0006 0xf115 LS_SERDES_CONTROL_1

1Ex0007 0x0000 LS_SERDES_CONTROL_2

1Ex0008 0x0000 LS_SERDES_CONTROL_3

1Ex0009 0x0380 HS_OVERLAY_CONTROL

1Ex000A 0x1fff LS_overlay _CONTROL

1Ex000B 0x0d10 loopback_TP_CONTROL

1Ex000C 0x0371 LS_CONFIG_CONTROL

1Ex000D 0x2f80 CLK_CONTROL

1Ex000E 0x0000 RESET_CONTROL

1Ex000F 0x70af CHANNEL_STATUS_1

1Ex0010 0x0000 HS_ERROR_COUNTER

1Ex0011 0x0000 LS_LN0_ERROR_COUNTER

1Ex0012 0x0000 LS_LN1_ERROR_COUNTER

1Ex0013 0x0000 LS_LN2_ERROR_COUNTER

1Ex0014 0x0000 LS_LN3_ERROR_COUNTER

1Ex0015 0x4142 LS_STATUS_1 (lane0)

1Ex0015 0x4142 LS_STATUS_1 (lane1)

1Ex0015 0x4142 LS_STATUS_1 (lane2)

1Ex0015 0x4142 LS_STATUS_1 (lane3)

1Ex0016 0xf006 HS_STATUS_1

1Ex0017 0x2000 dst_control_1

1Ex0018 0x0c20 dst_control_2

1Ex0019 0x2500 DSR_CONTROL_1

1Ex001A 0xac20 dsr_control_2

1Ex001B 0x1043 DATA_SWITCH_STATUS

1Ex001C 0x0000 LS_CH_CONTROL_1

1Ex001D 0x0000 HS_CH_CONTROL_1

1Ex001E 0x0000 EXT_ADDRESS_CONTROL

1Ex001F 0x0000 EXT_ADDRESS_DATA

1Ex8003 0x0283 VS_10G_LN_ALIGN_ACODE_P

1Ex8004 0x017c VS_10G_LN_ALIGN_ACODE_N

1Ex8021 0x000f MC_AUTO_CONTROL

1Ex802A 0x02fd dst_on_char_control

1Ex802B 0x02fd dst_off_char_control

1Ex802C 0x0207 dst_stamp_char_control

1Ex802D 0x02fd DSR_ON_char_control

1Ex802E 0x02fd DSR_OFF_char_control

1Ex802F 0x0207 DSR_STUFF_CHAR_CONTROL

1Ex8040 0x0000 LATENCY_MEASE_CONTROL

1Ex8041 0x0000 LATENCY_COUNTER_2

1Ex8042 0x0000 LATENCY_COUNTER_1

1Ex8100 0x0000 TRIGGER_LOAD_CONTROL

1Ex8101 0x0000 TRIGGER_EN_CONTROL

非常感谢提供任何调试此问题的建议。

非常感谢您的反馈和支持!

BR

Joerg