主题中讨论的其他器件:DP83TG720R-Q1、DP83TG720EVM-MC 、

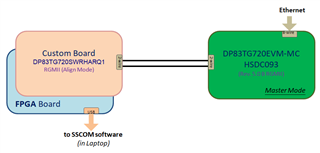

我们的团队正在评估 DP83TG720R-Q1 以太网 PHY (使用 A) 定制设计的电路板和 。 DP83TG720EVM-MC 评估板 .

设置如下:

- 评估板(EVM)连接 : DP83TG720EVM-MC 连接到以太网。

- 自定义电路板设置 :

- 。 开发板 也使用 DP83TG720R-Q1 .

- 。 定制电路板连接到 FPGA 、用作 MAC 接口 .

- 。 FPGA 通过 USB 连接到笔记本电脑 和 SSCOM 软件 用于监控通信。

- PHY ID 识别 :

- 。 正确检测到 PHY 在 SSCOM 中、意味着 MDIO 接口正在工作。它提供以下 msg:

配置网络接口...Zynq GEM:ff0e0000、MDIO 总线 ff0e0000、phyaddr 0、接口 RGMII-id

[17:32:49.368] in¡û¡ô[7.669787] macb ff0e0000.ethernet eth0:phy [ff0e0000.ethernet-ffffffff:00]驱动器[TI DP83TG720CS1.1](IRQ=poll)

[ 7.680170] macb ff0e0000.ethernet eth0:配置 phy/RGMII-id 链路模式 - 不过、 不会发生通信 或者、如果是、它会持续很短的时间(~10秒)。

- 。 正确检测到 PHY 在 SSCOM 中、意味着 MDIO 接口正在工作。它提供以下 msg:

- SSCOM 中的错误消息 :

- [17:34:17.463] in¡û¡ô[100.874880] macb ff0e0000.Ethernet eth0:链路接通- 1Gbps/满-流控关闭

- [17:34:27.681] in¡û¡ô[105.994103] macb ff0e0000.ethernet eth0:link is down

这表明 链接最初已建立、但稍后会断开 .

到目前为止已完成的故障排除:

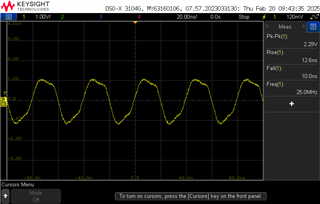

时钟信号已验证

- 。 25 MHz XTAL/时钟源 已检查 正确的频率、上升/下降时间、负载电容和阻抗匹配 .

已识别 PHY 地址

- 。 检测到 PHY ID MDIO 正确配置。

已检查 MDIO 通信

- FPGA 成功读取 PHY ID、从而确认 MDIO 和 MDC 信号工作正常。 不是吗?

已检查功率和电压电平

- 经验证 VDDIO (1.8V)、VDDA3P3和 VDD1P0 都在建议的范围内。

已验证搭接引脚和配置

- 确保正确 自举设置 以便 PHY 操作。 如果您有任何其他建议、我也可以尝试其他配置?

已验证端接电阻

- 已确认 100Ω 差分终端 存在电压纹波

-

向 TI 支持团队提问:

TRD_P 和 TRD_M 上的直流电压测量值

- 找到 1.65V、而不是预期的~1.1V 、建议可能存在的问题 信号完整性 .

观察到 PHY 链路稳定性问题

- 。 链路已建立、但在~10秒后断开 、如 SSCOM 日志中所示。

- 为什么链路会短暂建立(~10秒)然后断开?

- TRD_P/TRD_M 上的直流电压是否异常? 如果是、可能是什么原因造成的?

- 即使链路最初建立、阻抗不匹配或端接也会影响长期链路稳定性吗?

- 我们是否必须始终将 RESET_N 和 WAKE 引脚分别连接至1.8V 和3.3V?

- 此问题是否与 FPGA MAC 配置有关? MAC-PHY 正确交互是否需要特定设置?

e2e.ti.com/.../DP83TG720_5F00_Custom-Board.pdf

我附上了原理图供您参考。

对于 TI 提出的任何见解或调试建议、我们将不胜感激。

谢谢!