请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DS90UB935-Q1 工具与软件:

嗨、团队:

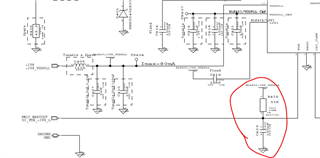

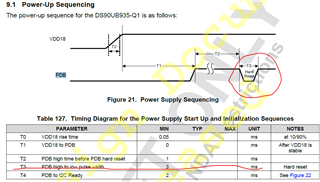

我的客户 Valeo 将 TPS650332x-Q1 RSTOUT 引脚连接到 DS90UB935的 PDB 引脚、并且他们使用 DS90UB935的 PDB 引脚中的 RC 电路、从而为 T3时序提供延迟。 但这会导致 PMIC 异常、而且该异常在移除 RC 后消失。 他们询问是否可以忽略 T3时序要求并移除 RC 电路。

此致、

Xiaowei Zhang