Other Parts Discussed in Thread: ALP

Thread 中讨论的其他器件:ALP

工具与软件:

您好!

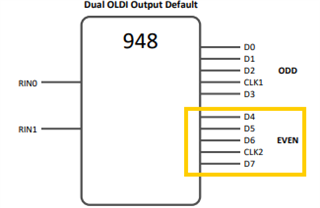

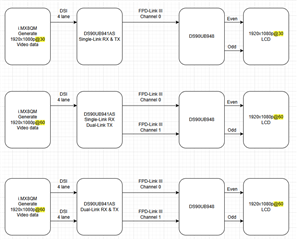

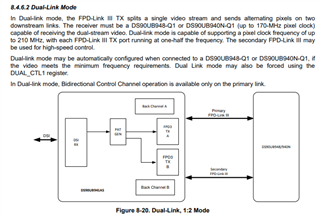

我准备好了 DS90UB941串行器和 DS90UB948解串器。 I 的 LCD 为1920x1080、所需的像素时钟为143MHz。 由于像素时钟高于105MHz、我需要使用双 DSI 输入。 我仍需解决器件树中的一些错误、因此我想先使用信号发生器测试 LCD。 941数据表具有 独立2:2模式的示例代码、但没有包含任何双模的代码、所以我不确定所有寄存器需要更改的地方。

您能否提供我需要设置的寄存器以便图形发生器与上述面板配合使用? 该面板的时序详细信息如下:

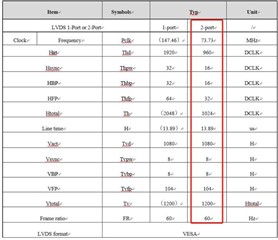

像素时钟:143.28 MHz (60Hz)

水平显示区域:1920

水平前沿:24.

水平后沿:70

HSYNC 总周期时间:2048

垂直显示区域:1080

垂直前沿:16

垂直后沿:48.

Vsync 总周期时间:1166

谢谢!