工具与软件:

你好

我询问是否可以收到 THVD9491-SEP (RS -485收发器)的内部电路图。

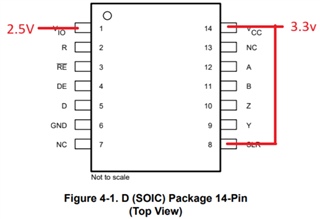

目前、我已按如下方式为 THVD9491-SEP 设计电路。 (我将用电源部分的简化图像代替实际的完整电路)

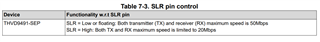

在图中可以看到、我已将 SLR 引脚连接到3.3V VCC 引脚、VIO 为2.5V。

SLR 引脚的输入电压允许范围为-0.3 < SLR < 2.7V (VIO + 0.2)。

由于我已经超过了输入电压允许的范围、更改设计是正确的、但在查看数据表后、我发现 VIO 引脚的输入电压允许范围为 VIO <3.5V (VCC + 0.2)。

从这种情况来看、即使 SLR 引脚可以输入高达3.7V 的电压、也不会有大问题。

正因如此、我想要提供芯片内部电路的相关信息、在不改变设计的情况下、看看芯片操作是否会有任何问题。

或者、如果无法做到、请告诉我、在 VIO 为2.5V 的情况下、SLR 引脚连接到3.3V 是否没有什么大不了的。

此致、

金女士