https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1478416/tusb1104-tusb1104

器件型号:TUSB1104工具与软件:

尊敬的先生/女士:

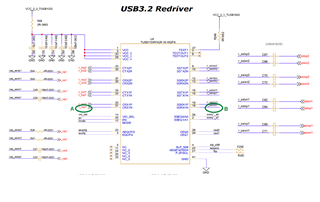

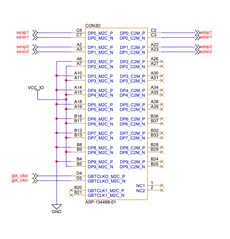

我们已使用 TI 转接驱动器 TUSB1104开发了 FMC 卡 、用于10Gbps、USB3.2、Gen2、2x2模式 IP 内核测试。 主机板将是 Xilinx、Altera、Lattice Semiconductor、Asmedia 高速 FPGA 主机卡。

我们需要清除 USB 合规性测试。

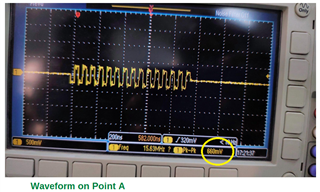

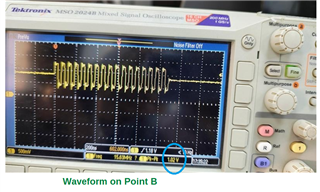

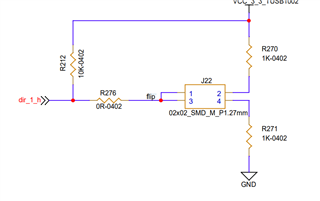

在引脚搭接模式下、我们得到的结果如下:

ASMedia Type C 端口+ Amphenol 电缆

Lane1->未枚举。 在枚举期间恢复。

Lane2-> USB20枚举

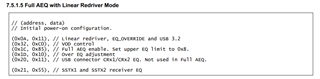

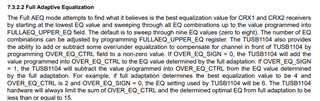

我们计划于2024年2月27日前往马来西亚进行合规性测试。根据数据表中所述 、在完全自适应均衡模式下、TUSB1104将自动确定其认为的最佳均衡设置。 在全 AEQ 模式下、无论通道是短通道、长通道还是介于两者之间、TUSB1104都会尝试确定最佳设置。 使用该模式。

因此、请指导我们如何使用此模式及其工作原理。 另外、请分享有关使用 完整 AEQ 模式的应用指南或程序。