请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83848Q-Q1 工具与软件:

尊敬的团队:

我的客户使用的是 DP83848Q-Q1。

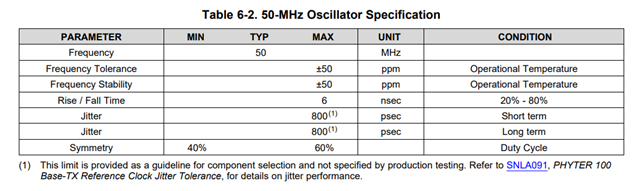

CPU 将50MHz 时钟输出到当前 DP83848Q-Q1的引脚28 (XI)。 RMII 通过检查时钟的风险来识别数据是否已同步、但如果时钟的占空比被破坏(例如、低占空比变得极短)、那么它是否会被建立为通信?

如果有低电平脉冲宽度的规格、请告诉我。

此致、

二宫幸志