Other Parts Discussed in Thread: DP83867IR

工具/软件:

您好、

这个问题是以下主题的延续。

e2e.ti.com/.../dp83867ir-reset-pulse-duration

当时、研究人员认为客户通过将持续时间 从 GPIO 干扰更改为 RESET_N 驱动为低电平来解决了 MDIO 读取问题。

然而、经过进一步调查、他们仍然很少看到这种现象。

根据调查、他们发现他们在 MDIO 线路上使用了一点强上拉电阻器。

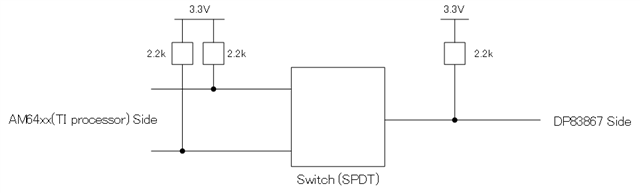

根据数据表、您建议对 MDIO 线路使用1.5k Ω。 但他们使用了1.1k Ω(实际上、客户配置如下。) 这一行中。

因此、他们移除了 DP83867侧2.2k PU 电阻、然后看起来此问题已解决。

但是、客户有以下问题。

*即使使用了1.1k Ω PU 电阻、他们也确认 MDIO 信号足够驱动至低电平(在"低电平"驱动信号的情况下、他们确认大约200mV)。

实际上、它们使用的 PU 电阻值高于建议值、不过它们可以满足 DP83867IR MDIO 的 VIL 规格。

因此、客户无法理解为什么他们认为问题已得到解决。

你有什么想法,为什么我们可以看到这样的差异?

此致、