工具/软件:

您好、我们使用的是 DP83867E 作为连接到 Jetson AGX Orin 的 RGMII PHY、并试图获得稳定的连接。

我们将 RX_CTRL 搭接至模式3、其余的搭接引脚设置为模式1。

在测试期间、我们能够通过使 RESET_N 引脚与 Jetson PHY_Reset 保持断开连接、并通过 RC 电路将 RESET_N 引脚连接到 VDDIO、从而获得网络链路、以便在短暂的延迟后、该引脚被上拉并保持高电平。 通过此设置、我们已验证我们的硬件设置是否正确、并能够成功实现 MDIO 通信和互联网连接。

在连接 Jetson PHY_Reset 时、我们会观察到一个问题、即交换 MDIO 消息失败并且复位线路被 Jetson 拉至低电平。

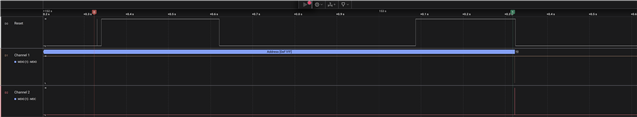

连接逻辑分析仪后、我们能够看到 Jetson PHY_Reset 行为和 MDIO 封装。 标记0是复位序列开始的位置。 标记1是指尝试进行 MDIO 通信。

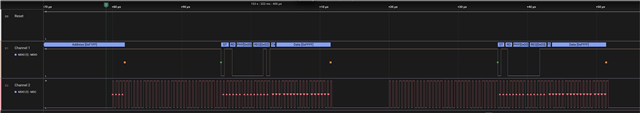

放大了尝试进行 MDIO 通信的部分:

Jetson 尝试读取寄存器0x02和0x03、但操作失败。 PHY 在转换期间不会下拉 MDIO 线路、并且读取0xFFFFF 值、即使此时复位为高电平也是如此。

什么可能 导致读取 MDIO 数据失败?

仅通过 RC 电路上拉 RESET_N 而不连接 Jetson 是否可行?