Other Parts Discussed in Thread: AM2432, DP83822I

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83822I 主题中讨论的其他器件:AM2432、

工具/软件:

尊敬的团队:

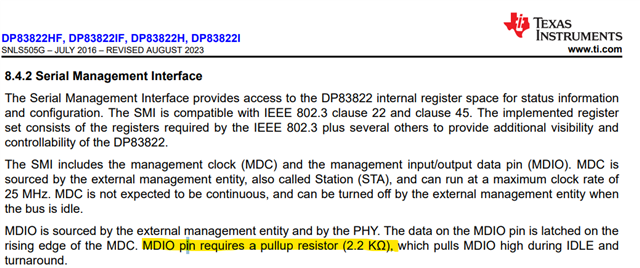

客户正在使用 AM2432 (PRU 单元 MDIO:无拉电阻)评估 DP83822I。

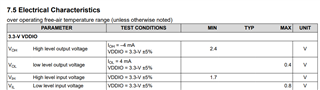

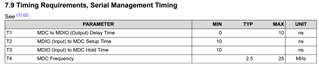

由于 DP83822I MDIO 的上拉电阻为4.7kΩ、因此当接通电源时、无法稳定读取 PHY 寄存器值。 这种现象很少见。

当他们根据 DP83822I 数据表将上拉电阻值从4.7kΩ 更改为2.2kΩ 时、这个现象就得到了解决。

为什么 MDIO 上拉电阻值是2.2kΩ?

如果 MDIO 上拉电阻值为4.7kΩ、您会想到什么问题?

此致、

二宫幸史