Other Parts Discussed in Thread: TCA9406, TCA9548A

Thread 中讨论的其他器件: TCA9548A

工具/软件:

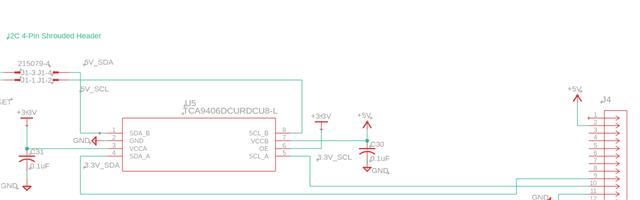

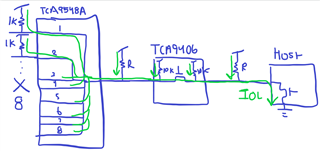

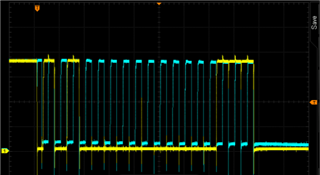

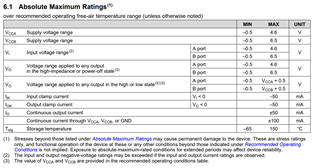

我们使用 TCA9406从3.3V 转换到5V、并且看到似乎随机的故障、其中 SDA 或 SCL 线(在 A 侧或 B 侧)相对于接地测量出低电阻(50 Ω 至140 Ω)。 这会使任何连接的器件无法控制总线、因为信号保持在~0.8V 的低电压下。

主器件侧是一个非板载 FPGA、连接到另一个 TCA9406用于1.8V 至3.3V 转换、5V 侧是一个非板载微控制器。 我们在3.3V 侧使用2个链式 TCA IC 上的内部上拉电阻、而5V 侧在 MCU 上具有~20k Ω 的内部上拉电阻。

这些器件不是热插拔、但会任意进行下电上电。 它们通常运行良好、在初始启动和安装期间正常运行、但似乎自发失败、可能是在进行下电上电后、也可能是在操作过程中。 应该注意的是、我们已将 OE 连接至 VCCA、因此器件在下电上电期间不会被禁用。

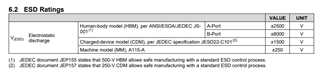

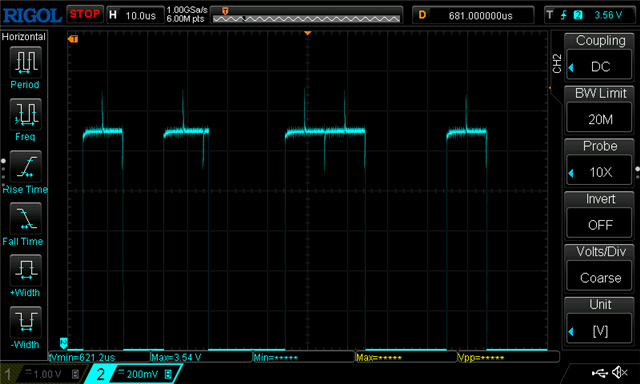

显然、器件会受到一些损坏、但不清楚这种情况会如何发生。 电源通常管理良好、很奇怪的是器件会自动发生故障。 我猜最好的是一些 ESD 损坏会削弱器件、以及一些最终导致的瞬态浪涌? 不过、我已经捕获了启动和下降序列、它们很好且干净~2ms 的斜升。

我们正在考虑仅仅更改器件和通信方案(UART)、但我们非常希望就缓解这些故障的可能短期建议提供任何指导。