Other Parts Discussed in Thread: DS90CF364

工具/软件:

您好团队:

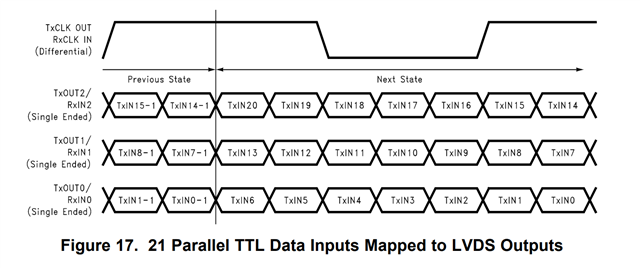

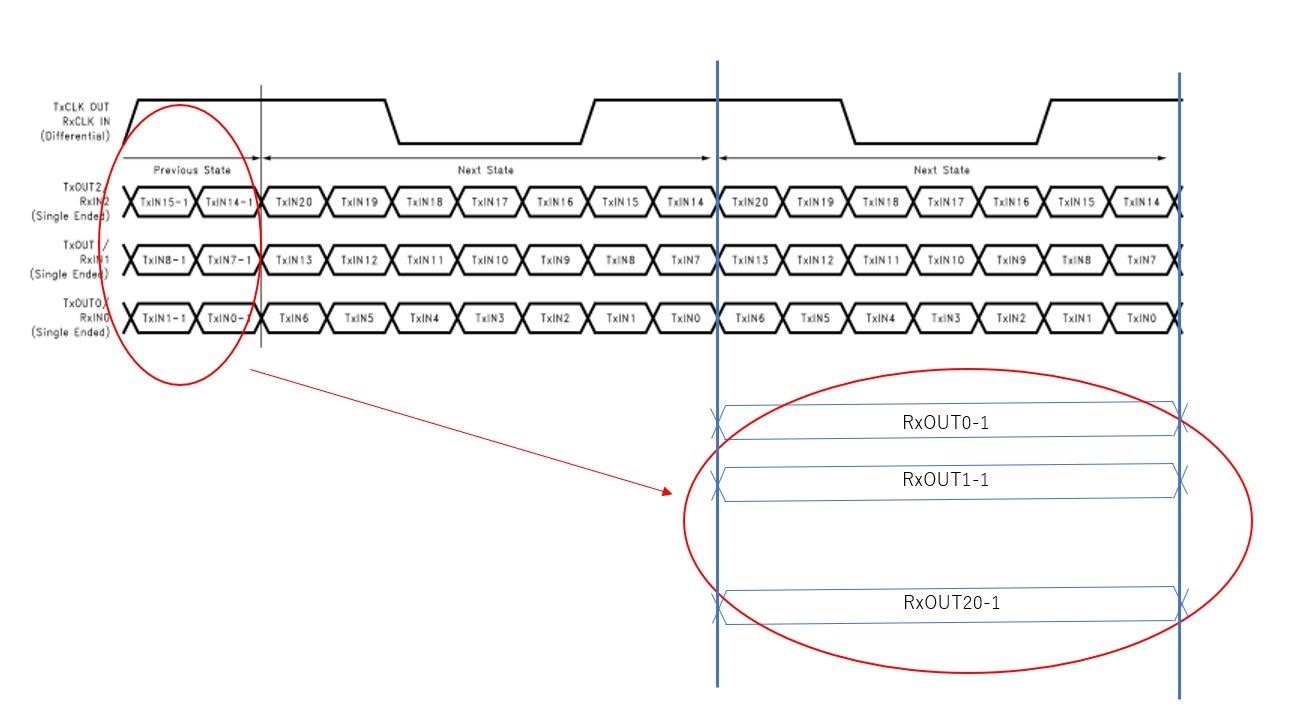

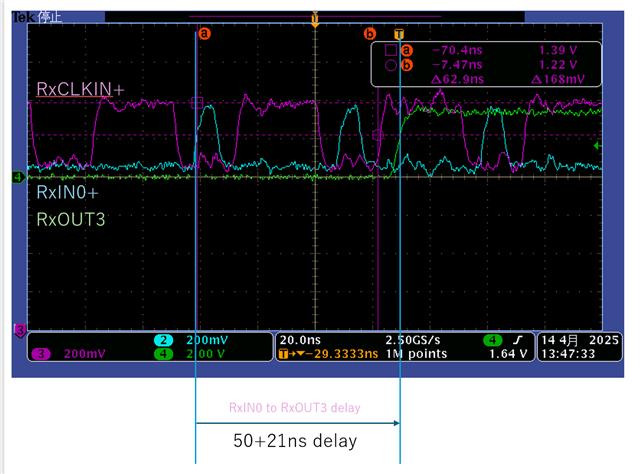

客户想澄清 DS90CF364的 RxIN0到 RxOUT 延迟时间。

客户为 RxCLK 使用20mH 时钟。 它们测量了延迟时间、如下所示。

RxIN0到 RxOUT0延迟时间:50ns (1个周期)

RxIN0到 RxOUT3的延迟时间:50ns+21ns

波形如下。

/cfs-file/__key/communityserver-discussions-components-files/138/DS90CF364_5F00_waveform.pptx

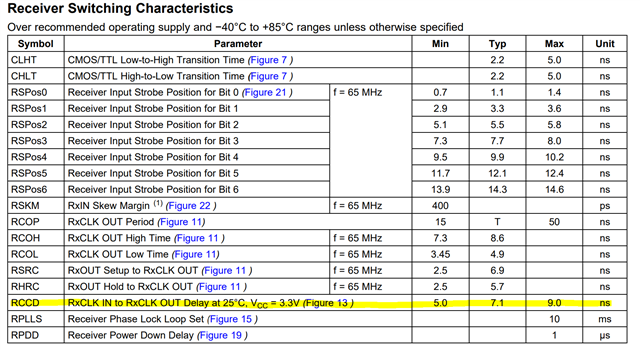

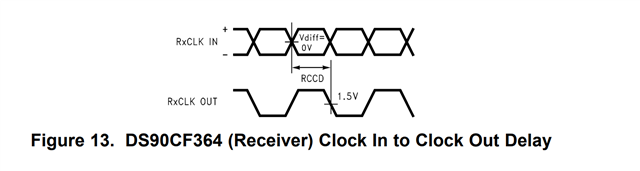

该延迟时间是否合适? 此外、我和客户不知道 DS90CF364的数据表中提供了这个延迟、因此您想告知数据表中哪个部分描述了这个延迟?

感谢您的建议。

此致、

Tamazaki Akihisa