工具/软件:

您好的团队、

客户无法通过以下过程和设置查看合规性测试的波形。

合规性目标:10BASE-T

编程步骤

1.禁用自动协商:BMCR_Register 位12 0x0

2.选择10Mbps:BMCR_Register 位13 0x0

3.通过 COMPT_Register 选择模式:1001或0100或0011

BTW、客户注意到电压斜坡可能是一个问题。 如果 T1或 T3在0.5ms 过去之前斜升、会发生什么情况?

此致、

Hayashi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好的团队、

客户无法通过以下过程和设置查看合规性测试的波形。

合规性目标:10BASE-T

编程步骤

1.禁用自动协商:BMCR_Register 位12 0x0

2.选择10Mbps:BMCR_Register 位13 0x0

3.通过 COMPT_Register 选择模式:1001或0100或0011

BTW、客户注意到电压斜坡可能是一个问题。 如果 T1或 T3在0.5ms 过去之前斜升、会发生什么情况?

此致、

Hayashi

Hayashi-San

对于合规性测试、请参阅该应用手册 https://www.ti.com/lit/an/snla266b/snla266b.pdf。

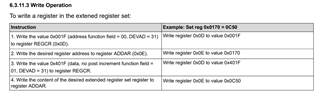

由于 COMPT_Register 是扩展寄存器、它们是否遵循扩展寄存器读取和写入过程?

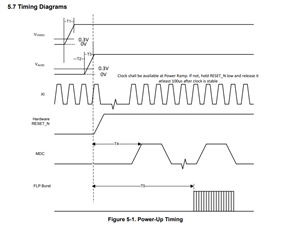

您能分享一下它们的上电顺序图吗? 它们必须满足 DP83825上电时序要求、否则无法保证器件正常运行。

谢谢

David

您好、David:

我是日本 AFAE 的 Kurumi、我从 Hayashi-San 接管了这个账户。

对于扩展的寄存器读写过程、是否意味着我们需要在"禁用自动协商:BMCR_Register bit12 0x0"之前执行这4个步骤?

对于上电序列、它们对 AVDD 和 VDDIO 使用相同的3.3V 电压。 这会是个问题吗?

此外、3.3V 线路可能会过快、即0.27ms 的电压斜坡持续时间。 3.3V 来自 PMIC、客户无法更改设置。 因此、我认为我们需要外部电路来使其变慢。 可能的选项是什么? 正在使用 RC 滤波器? 您碰巧知道其他方法吗?

此致、

Kurumi

Kurumi-San

请在下面查看我的答复

对于扩展的寄存器读写过程、是否意味着我们需要在"禁用自动协商:BMCR_Register bit12 0x0"之前执行这4个步骤?

请查看下面的脚本。 4个步骤是写入寄存器0x27、因此您需要在写入寄存器0x1F 和0x0后执行此操作。

对于上电序列、它们对 AVDD 和 VDDIO 使用相同的3.3V 电压。 这会是个问题吗?

不、但我想确保它们符合 DP83825的上电序列、如下所示。

谢谢

David

您好、David:

非常感谢您对扩展寄存器的额外说明。 客户确认信号通信正常。

对于电源序列、我认为对 AVDD 和 VDDIO 使用相同的3.3V 电压是可以的。 但 电压斜坡持续时间应处于数据表规格范围内、即0.5ms。 3.3V 线路现在的斜坡持续时间似乎为0.27ms。 如前所述、持续时间来自 PMIC 设置、客户无法更改该设置。 我让他们添加 RC 滤波器、但这也是不可接受的。 您是否知道任何其他可能的方法来实现0.5ms 的持续时间?

此致、

Kurumi