主题:DP83869中讨论的其他器件

工具/软件:

您好、

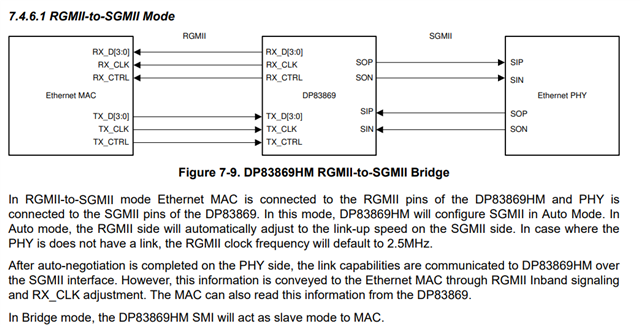

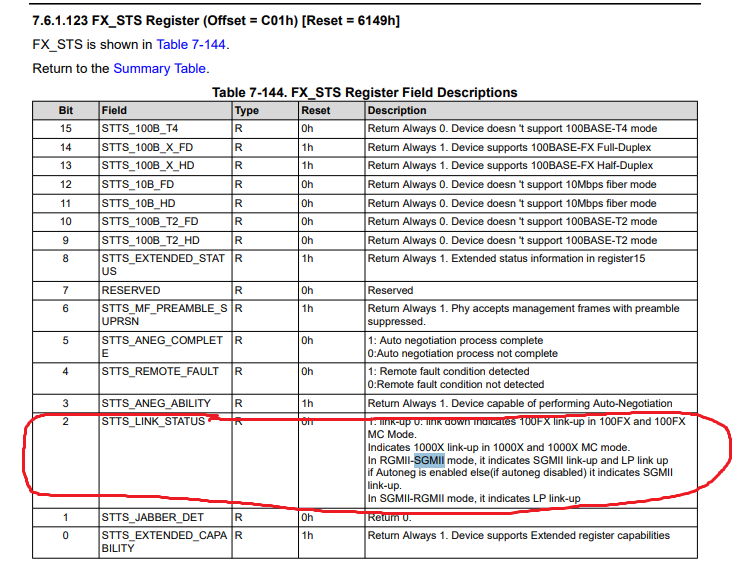

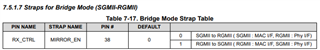

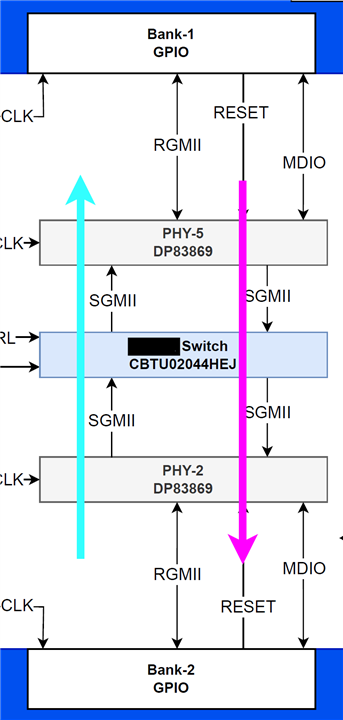

我目前正在对一个设计进行故障排除、我们试图在 SGMII 背对背配置中使用 PHY 在两个 FPGA 之间建立单向通信。 通过断开与正在传输数据的 FPGA 相对应的 RX SGMII 差分对来强制进行单向通信。

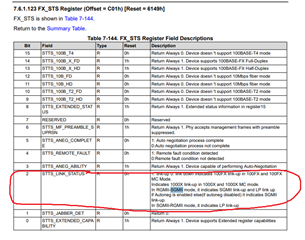

我们已经使用示波器探测 FPGA 的 TX 时钟信号、测得的频率为125 MHz。 这是正确的、因为 MAC 接口的配置链路速度为1000Mbps。 PHY 的 RX 时钟信号的频率为2.5 MHz、我假设这意味着未建立链路或发生其他一些问题。

请参阅下面的问题列表。

1.这种 SGMII 背对背配置是否可行?

2. PHY 之间连接的4个信号中只有2个可以正常工作吗?

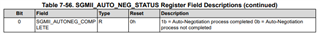

3.是否需要任何特殊的寄存器配置才能使其正常工作? 我在一篇旧论坛帖子中读到、其中提到需要禁用自动协商功能。

4、实现 MII 环回模式的工作步骤是什么? 我无法使该模式正常工作。

谢谢、

Jean