工具/软件:

您好、

我 在我们的产品中使用 DP83869HMRGZT 器件、我们面临初始化问题。 调试时发现、LED0引脚仅为高电平状态、即使具有下拉电阻(2.49k 至 GND)也是如此。

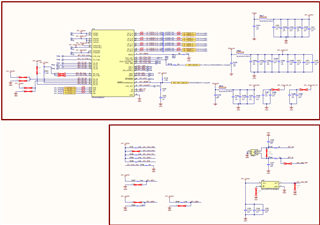

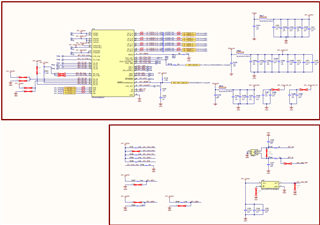

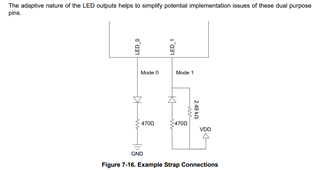

这是我们的原理图供您参考、

如有需要、请告知我进一步的详细信息。

提前感谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好、

我 在我们的产品中使用 DP83869HMRGZT 器件、我们面临初始化问题。 调试时发现、LED0引脚仅为高电平状态、即使具有下拉电阻(2.49k 至 GND)也是如此。

这是我们的原理图供您参考、

如有需要、请告知我进一步的详细信息。

提前感谢。

尊敬的 Mani:

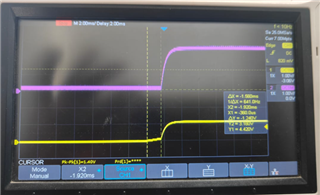

何时为 VDD1P1供电?

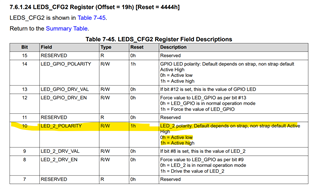

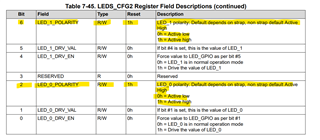

Reg- 0X0019:4004

reg- 0X01DF:0044

看起来 根据您的设置、LED 极性已正确设置为低电平有效。 如果您想使其处于高电平有效状态、请将其配置为 GND 而不是 VDDIO。

似乎结果正常、但我们仍然面临 SFP 初始化问题。 您能否告诉我们下一个要继续的检查点。

SFP 初始化的具体问题是什么?

此致、

j

VDD1P1和 VDD2P5同时供电。

j 说: 如果您想使其处于高电平有效状态、请将其配置为 GND 而不是 VDDIO。

制造商: 哪个 LED 自举引脚将设置为下拉电阻

j 说: SFP 初始化的具体问题是什么?

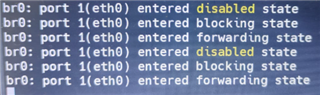

我们已将此 SFP 转换器连接到 KSZ9477交换机 IC。 我们已尝试通过 SFP 转换器 IC 通过光纤 ping KSZ 交换机 IC。 但 Ping 未发生、并且在命令窗口中收到以下消息、

如果可能、我们可以连接一个小的同步电路来短路问题、

邮件 ID: manigandans@iinvsys.com

BR、

Mani

尊敬的 Mani:

LED 引脚会对引脚是否搭接至 GND 或 VDDIO 进行采样、并根据搭接来更改其极性、因为 LED 引脚也用作 PHY 内部功能的跳线。

以下是配置示例:

如果希望保持电流搭接设置、则可以写入寄存器19h 的位2、6、10。

而且、目前我似乎没有足够的信息来进行短暂的同步。

您能否将 C00h 的寄存器转储发送到 C30h、以便更好地了解与 PHY 的光纤链路内部发生了什么情况?

您是否还能向我们发送与 SFP 固定框架连接的示意图?

这是仅在一个 PHY 还是多个 PHY 上发生的?

此致、

j