工具/软件:

尊敬的 TI 专家:

我的客户在他们的客户端遇到了一个问题

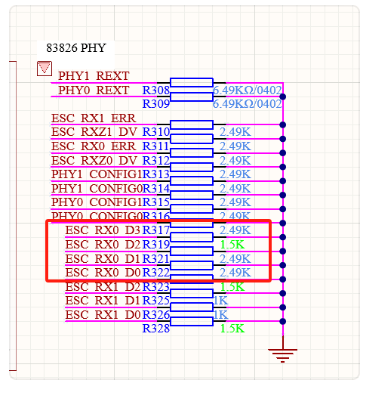

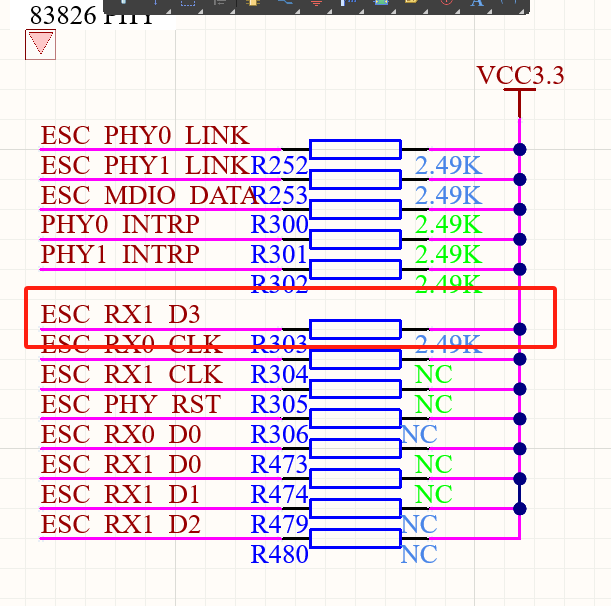

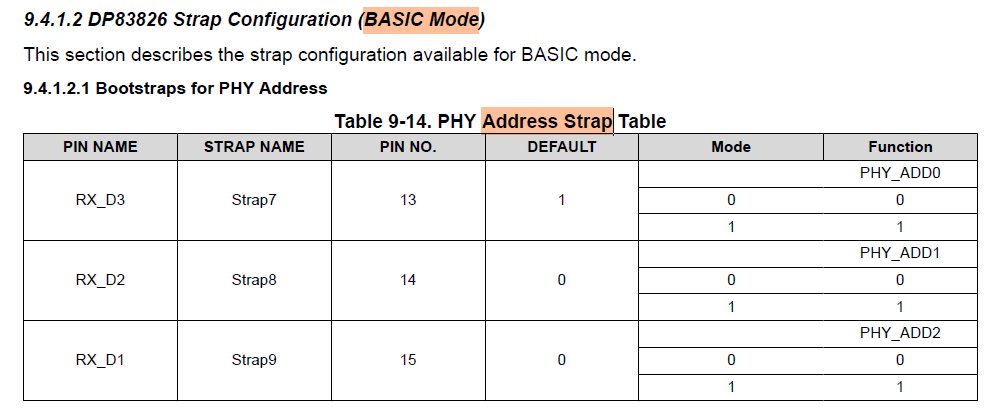

它们在伺服产品中使用两款 DP83826I。 他们现在发现、当机器 POR 时、MCU 可能无法读取 PHY_ADDRESS (RX1_D3)的高电压电平状态。

概率为100台机器中的5台。 签发机使用。 概率为100倍 POR 的20-30倍。

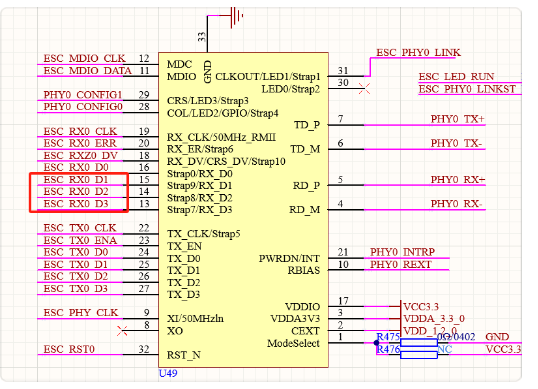

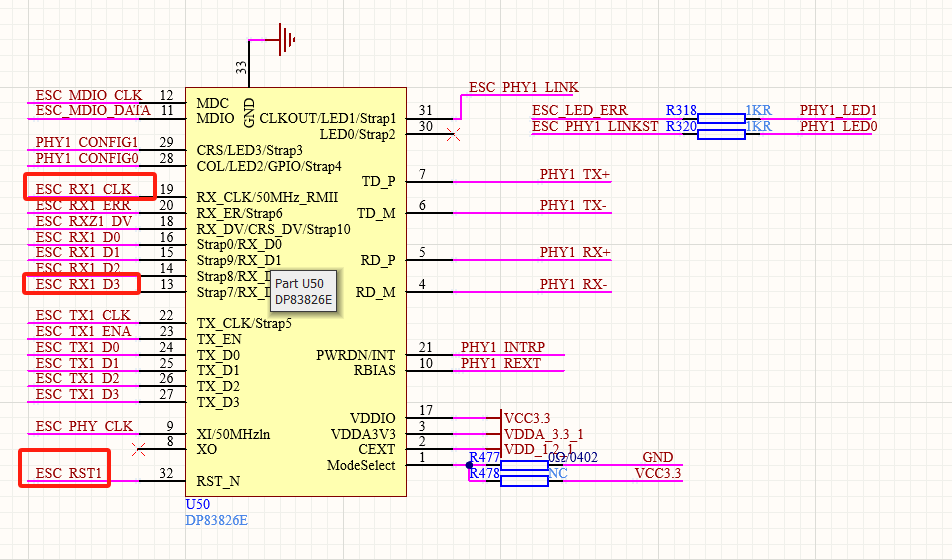

大家可以看到、它们使用2个 DP83826I、即 U49和 U50。 两者都以基本模式运行。 (Strap 配置6连接 GND)。

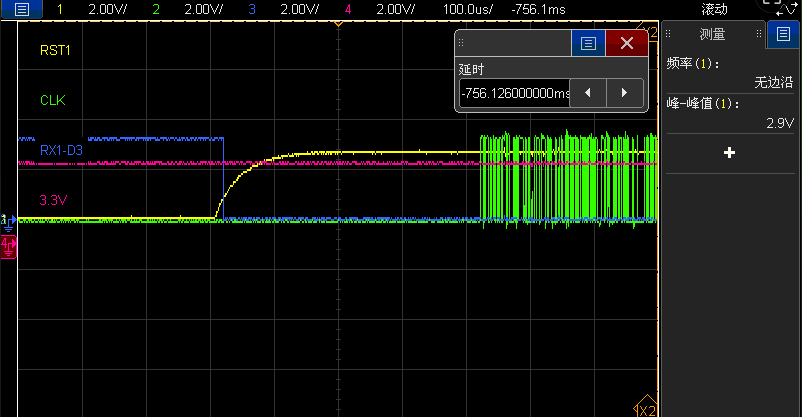

RX_D3应为高电压电平。 但当 RESET 信号上升时、它会下降。

Q1:当复位信号上升时、RX1_D3 (来自 U50)为什么会下降。 这将导致 MCU 收到 RX1_D3的错误状态(低电压电平、该状态应为高电压电平)。

问题2: 为什么时钟信号仅在复位信号变为高电平后才出现?