工具/软件:

您好、

我们当前在 LLC 谐振转换器中使用 UCC24624、并面临一个问题、即 SR MOSFET 栅极会在漏极电流达到零之前关断。 这会导致体二极管长时间导通、从而增加功率损耗和发热。

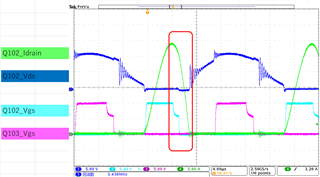

如随附的波形(以红色突出显示)所示、在栅极关断时仍然存在很大的漏极电流。

根据数据表、我们怀疑这是由于固定的 VTHVGOFF = 10.5mV 关断阈值所致。

我们已经在 VSS 引脚和 MOSFET 源极之间采用了建议的电阻器来增加关断阈值、但没有观察到明显改善。

我们感谢您在以下方面提供指导:

-

这种早期关断行为通常是否属于寄生电感或与 MOSFET 封装相关的效应?

-

除了调整 VSS 阈值之外、是否还有其他可能更有效的对策?

-

您是否有关于 VD 布局(例如 PCB/PGND 或 VSS 布线)的任何建议以帮助缓解该问题?

非常感谢您的支持。

Conor