工具/软件:

您好:

我们正在仿真 RGMII 接口以实现 1Gbps 速度。

请向我们提供 以下数据

- RX (RXC、RD0、RD1、RD2、RD3 RX_CTL) RGMII PHY 处的信号在 PHY IBIS 模型的输入端、我应考虑的电压值是多少? (适用于 3V3 IO 模型和 1V8 IO 模型)

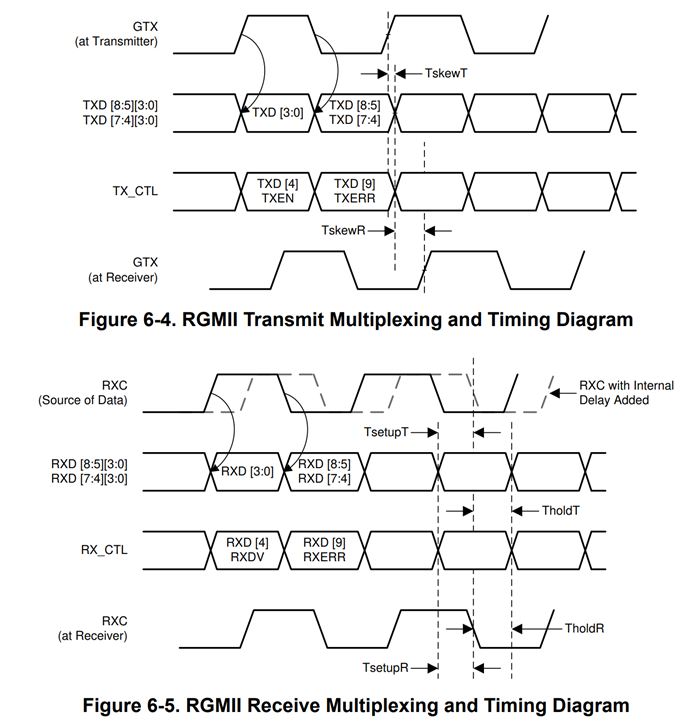

- RX_CTL 和 TX_CTL 信号的切换频率有多高、是否与 DATA 信号相同? 从 PHY 数据表中获取的以下时序图中可以看出、CTL 信号的切换也与数据信号的切换相同。

此致

Keshav