Other Parts Discussed in Thread: DP83867E

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83867E 工具/软件:

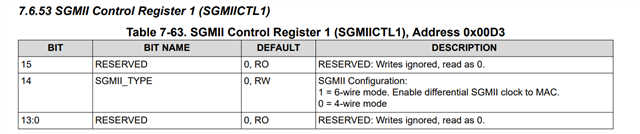

DP83867E SGMII EVM 评估板具有一个 SGMII 接口、该接口包含一个发送差分通道、一个接收差分通道和一个时钟差分通道。 我想移除时钟的差分通道、以便 SGMII 接口将时钟嵌入到数据流中。 如何实现该配置? 请告诉我必须修改 DP83867E 的所有寄存器以及修改内容、

此致、

Jaidev