Other Parts Discussed in Thread: DP83867E

工具/软件:

尊敬的所有人:

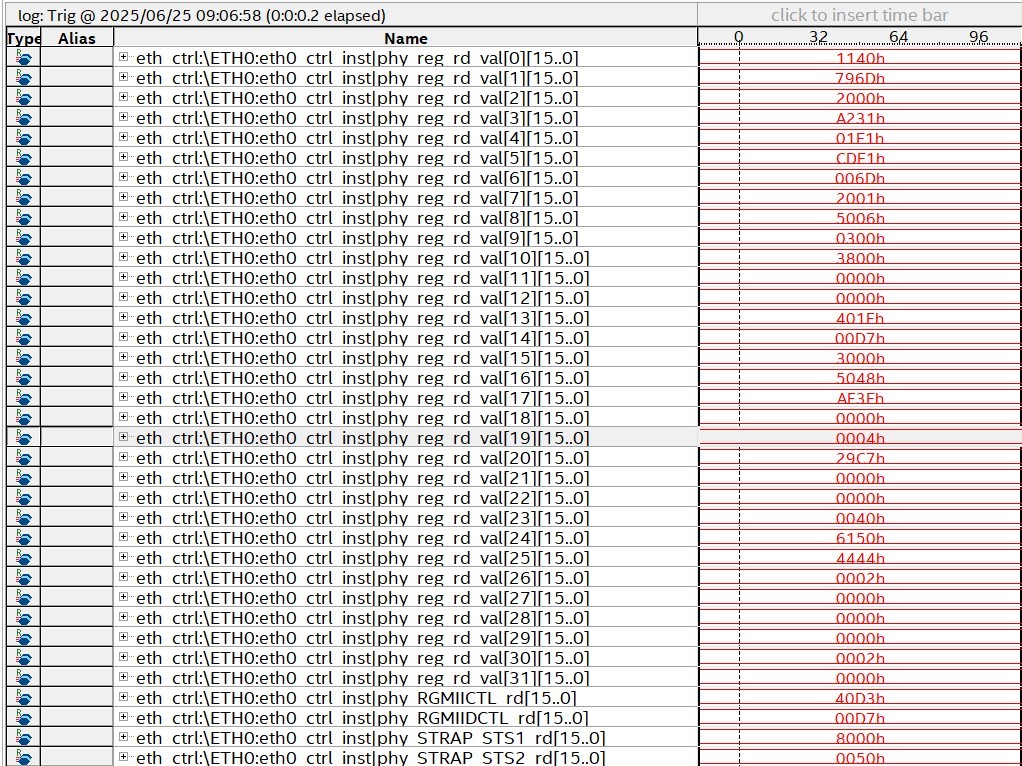

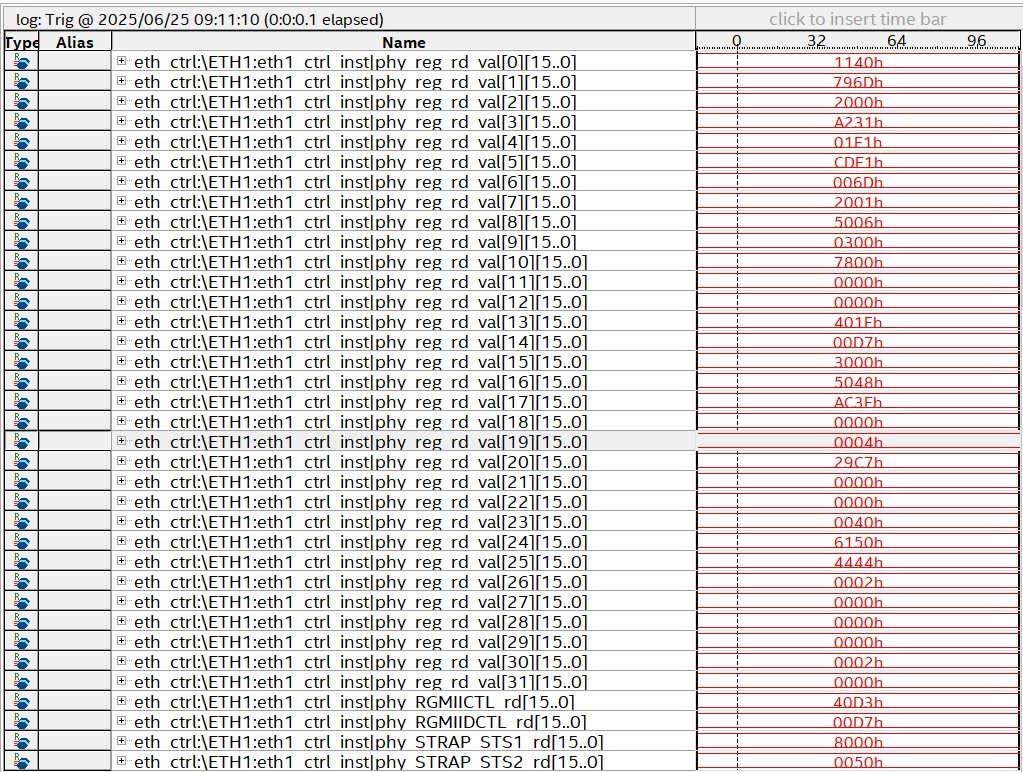

我们目前正在调试使用两个 Dp83867E 以太网收发器的 Cyclon V FPGA(商用以太网 IP 块)设计。

问题是 xGMII 错误中断、它会阻止在 PHU 和 FPGA 本身之间使用 IC 的内部环回函数进行测试。

在 10Mbits 下、我们会将数据传输到物理层、但不会以更高的速度传输。

时钟在规格范围内是稳定和精确的。 在 XI 和 XO 处检查。

FPGA - dp83867e RX/TX 布线长度完全在延迟规格范围内、长度差异小于 0.256mm。

xGMII 错误复位后会立即重新出现。

对于如何解释 xRGMII 错误中断有什么好的建议?