您好、

您能否介绍一下下面 1G PCS 主模式中的传统扰频器模式?

A.旧扰频器模式与正常扰频器模式之间的差异

b.旧扰频器模式扰频方法详细信息

C.选择传统扰频器模式的触发器

D.错误检测到旧扰频器模式的条件

E.如何防止检测传统扰频器模式(仅限如何在正常扰频模式下工作)

f.如果知道、在传统扰频器模式下运行的竞争器件型号

g.传统扰频器模式 TI 是否知识产权?

此致、

KATO

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、

您能否介绍一下下面 1G PCS 主模式中的传统扰频器模式?

A.旧扰频器模式与正常扰频器模式之间的差异

b.旧扰频器模式扰频方法详细信息

C.选择传统扰频器模式的触发器

D.错误检测到旧扰频器模式的条件

E.如何防止检测传统扰频器模式(仅限如何在正常扰频模式下工作)

f.如果知道、在传统扰频器模式下运行的竞争器件型号

g.传统扰频器模式 TI 是否知识产权?

此致、

KATO

尊敬的 Kato:

这里有一个 类似的 E2E 主题正在处理中、涵盖了大多数这些问题。 这是否与链接的线程相关?

e.您是否注意到 PHY 在与链路伙伴连接时启用了传统扰频模式? 但情况不应如此、但您可以尝试按照链接线程中的说明将 0x50 位 1 设置为“0"。“。

f.我不知道有任何竞争器件型号在传统扰频器模式下运行。 该模式似乎旨在用于特定 PHY 的测试。 我不确定是哪个 PHY、但正常运行时不应使用传统模式。

g.我需要进一步研究这一点。 我建议仅在正常编码模式下运行 PHY、因为这是预期用途。

此致、

Shane

尊敬的 Shane-San:

感谢您的快速答复。

是的、我的帖子是与链接的主题相关的问题。

尚未更新、我们的客户非常沮丧、因此、您能告诉我们一周内的旧扰频器模式详细信息吗?

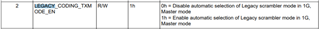

我发现较新的 DP83869HM 具有禁用传统扰频器模式自动选择的功能、即 legacy_coding_TXMODE_EN 寄存器。 因此、请确认 DP83867IS 是否具有与隐藏寄存器相同的功能、并考虑再次回答我上面的问题 a 至 g。

如果您能快速给我一些建议、将会很有帮助。

此致、

KATO

尊敬的 Kato:

我从链接的 E2E 主题中看到、当通信工作时、PHY 处于正常模式、当通信不良时、会恢复到传统模式。 当您看到这些通信问题且 PHY 切换到传统模式时、是否正在运行特定的测试?

您能否以 pdf 格式分享 DP83867 实施原理图? 我想看看您是否正确配置了此器件。 如果您想私下分享、您可以接受我的友谊申请、并在 E2E 上使用直接留言功能。 这将创建一个仅供您和我查看的单独空格:

可能存在与扰频器模式无关的实现问题。 通过查看原理图和布局、我们可以在传统模式与正常模式之间缩小范围之前排除这一点。 同时、我将通过链接中的 E2E 帖子与 Vivaan 合作、从而详细了解传统模式。

此致、

Shane

尊敬的 Kato-San:

感谢您提供的信息。 我正在内部研究传统模式、因此在此期间、让我们尝试一些可能有所帮助的操作:

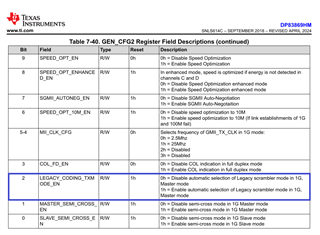

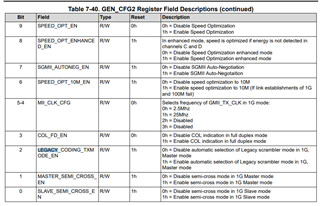

1.尝试将寄存器偏移 0x14h 位 2 设置为“0"。“。 我在 DP83869 数据表中意识到了这一点、但是有时这些器件会共享并非总是记录在案的寄存器。 我想看看这是否会阻止在 PHY 上启用传统模式:

2.您可以尝试降低振荡器/时钟缓冲器输出与 PHY XI 引脚之间的电阻吗? 120 欧姆电阻可能会干扰到发送到 PHY 的时钟信号。 我建议降低到大约 20 欧姆。

3.是否有任何符合我们数据表规格的磁性元件引脚对引脚替代产品 (48F-76NWZ2NL)? 就像我在私信中提到的、该部分不在此 PHY 的数据表规格范围内。 我无法找到该器件数据表、因此我基于 之前 使用同一器件的设计:

此致、

Shane

尊敬的 Kato-San:

1.是的、DP83867 存在相同的寄存器。 请将此设置为“0",“,以便、以便在 DP83867 处于主模式时禁用自动进入传统模式。

有关此模式的更多上下文:

-传统扰频器模式更改扰频器设置、并阻止 DP83867 与标准链路伙伴之间的通信。

-它旨在支持一些不符合标准链路建立协商程序的旧以太网 PHY。

-如果 DP83867 无法在主模式下保持链路、它将自动返回此模式。

2/3。 感谢您将此内容传达给客户。 我们只验证这些器件是否符合数据表规格、因此如果违反数据表规格、我们无法保证器件正常工作。

此致、

Shane

尊敬的 Kato-San:

此外、客户正在通过将 0x50 位 1 设置为“0"进行“进行测试。 我们明天将获得结果。

应设置的寄存器是 0x14h 位 2、而不是 0x50 位 1。 仅当 DP83867 处于从模式时、0x50 位 1 寄存器才相关。 在主模式下、这可能不会产生任何影响。

什么会触发传统扰频器模式的选择?

如果 PHY 在正常模式下建立链路时遇到问题、可恢复到传统扰频器模式。 我建议尝试使用 DP83867 EVM 连接 STB。 我们已经测试此 EVM 的工作原理、因此这样做有助于确定这是与 DRX 板相关的问题还是与器件相关的问题

此致、

Shane

尊敬的 Shane-San:

很抱歉让您困惑。

以上是一个拼写错误。 实际上、客户正在通过将 0x14 位 2 设置为“0"来“来进行测试。 我知道主模式的权变措施为 0x14 位 2、从模式的权变措施为 0x50 位 1、以避免转换到传统扰频器模式。 所以,事实证明是一个幸运的休息。

遗憾的是、我没有 DP83867ERGZ-S-EVM。 我将确认客户是否拥有它。 如果 DP83867 在正常模式下无法启动链路、可能的原因是什么? 如果你能给我一些可能的原因的例子,我将不胜感激。

此致、

KATO

尊敬的 Kato-San:

如果 DP83867 在正常模式下无法启动链接、可能的原因是什么?

链路问题可能源于磁性元件、MDI 布线、返回路径、EMI 等问题。 我担心的一个问题是、您的磁性元件超出了数据表规格。

如果还有其他建议我们应该尝试、任何建议都将非常有帮助。

我建议使用此权变措施在 DRX 和 STB 之间进行广泛测试。 如果问题完全消失、那么 PHY 可能已切换到传统模式、而没有出现实际的链路问题。 如果您能让我了解该测试的最新进展、我将不胜感激。

此致、

Shane

尊敬的 Shane-San:

由于应用了在 DRX 和 STB 之间将 0x14 位 2 设置为“0"的“的权变措施、因此继续建立链路、STB 会响应所有 ping 请求。 您担心、DP83867IS 可能已从正常扰频器模式切换到传统扰频器模式、而没有出现实际的链路问题。 我曾假设会有这样的情况:它不会响应 ping 请求、但我的猜测是错误的。 然后、您能否说明在主模式下转换到传统扰频器模式的详细检测方法?

我又问过客户、但他没有 EVM。 那么、我想确认一下情况、但客户是否应该购买 DP83867ERGZ-S-EVM?

此外、您过去使用相同磁性元件 (48F-76NWZ2NL) 时是否遇到过类似的链路问题?

此致、

KATO

尊敬的 Kato-San:

您能否解释在主模式下转换到传统扰频器模式的详细检测方法?

我需要在内部进行研究。 我将在下周中下班、所以我会请同事帮助推动这项工作、直到那时为止。

我想确认以防万一、但客户是否应该购买 DP83867ERGZ-S-EVM?

这是由客户决定的。 EVM 可以作为良好的性能基准、也是如何实现 DP83867 的参考。 如果客户对其电路板能够正常工作感到满意、则可能无需使用 EVM 进行测试。

此外、您过去是否使用相同磁性元件 (48F-76NWZ2NL) 遇到过类似的链路问题?

我在上一次回复中只看到了链接中的 E2E 主题。 他们使用了相同的磁性元件、并且在 LAN 测试中未通过某些项目。 您可以 通读该主题以了解更多详细信息。

此致、

Shane

尊敬的 Shane-San:

感谢您的信息。

有关在主模式下转换到传统扰频器模式的详细检测方法、我期待很快收到同事的更新。

对于传统扰频器模式、我在 DP83845 数据表第 48 页中找到了“3.22 不兼容互操作性模式“。 我认为可能是同一个功能。 所以,如果你能告诉我的细节,我会很感激。

我将与我们的客户讨论他们是否应该购买 DP83867ERGZ-S-EVM。

此致、

KATO

尊敬的 Kato-San:

有关在主模式下转换到传统扰频器模式的详细检测方法、我期待很快收到同事的更新。

在内部讨论后、DP83867 默认将尝试在正常模式和传统模式下进行链接。 PHY 解析为可以实现链路的任何模式。 在传统模式下应该能够与 DP83867 链接的唯一 PHY 是较旧的 Broadcom PHY、因此我不知道 STB 会将 867 置于此模式的原因。 我首先要检查的是您的磁性元件是否超出规格。 如果您可以使用符合我们规格的不同磁性元件进行测试、这将是不错的选择。

仅供参考、禁用传统模式没有风险。 如果客户 能够禁用此模式、则功能应正常。

对于传统扰频器模式、我在 DP83845 数据表的第 48 页上找到了“ 3.22 不兼容互操作性模式“。 我认为可能是同一个功能。 所以,如果你能告诉我细节,我会很感激。

是的、我认为这与传统模式的功能相同。 它旨在支持与未使用标准链路建立过程的旧 Broadcom PHY 的链路:

我的理解是否正确:在自动协商完成后、EVM 可以使用 USB-MDIO 接口检查任何寄存器、而无需连接 MAC I/F?

是的、正确。 您无需连接 MAC 接口即可在 MDI 侧完成自动协商、也无需通过 MDIO 线路读取我们的 PHY 寄存器。 您将需要一个外部 MSP430 来使用 USB-MDIO 进行连接、如本网页上所述。

连接到时钟缓冲器输出的阻尼电阻器已从 120Ω 更改为 33Ω、但症状已复制。

感谢您查看此内容。 阻尼电阻似乎不是导致此行为的原因。

此致、

Shane

尊敬的 Shane-San:

感谢您的信息。

我们将购买 DP83867ERGZ-S-EVM 和 MSP-EXP430F5529LP 并将其租赁给客户。 然后、客户将在 DP83867ERGZ-S-EVM 和 STB 之间进行连接、并在自动协商完成后使用 USB-MDIO 接口确认任何寄存器、而无需连接 MAC I/F

如果重复出现相同的症状、则原因可能是硬件。

此外、客户还可以在 DRX 和 DP83867ERGZ-S-EVM 之间进行连接并进行确认。

此致、

KATO

尊敬的 Kato-San:

从寄存器转储中、我可以看到 PHY 处于主器件旧模式、并且链路不会像您所描述的那样建立。 如果是在 EVM 上、则表明该行为与客户的系统无关、这可能是由于 STB PHY 与 DP83867 的连接方式所致。

如果您可以、我可以尝试在我们的实验中重现此行为并研究导致此行为的原因。 客户是否愿意向我们的达拉斯工厂发送 STB 电路板?

此致、

Shane